# — **Virtual Platforms for System Architecture, Development, and Test**

Dr Jakob Engblom, Cadence, [engblom@cadence.com](mailto:engblom@cadence.com)

**cadence**<sup>®</sup>

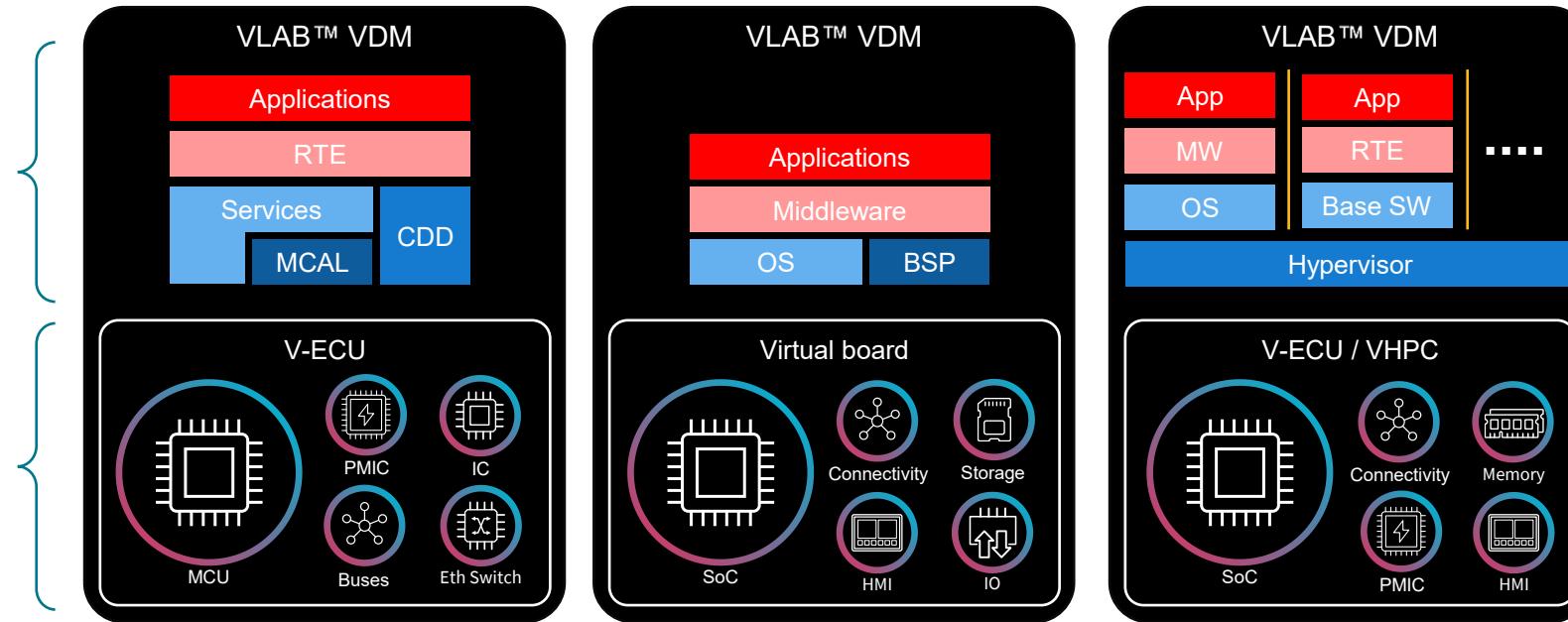

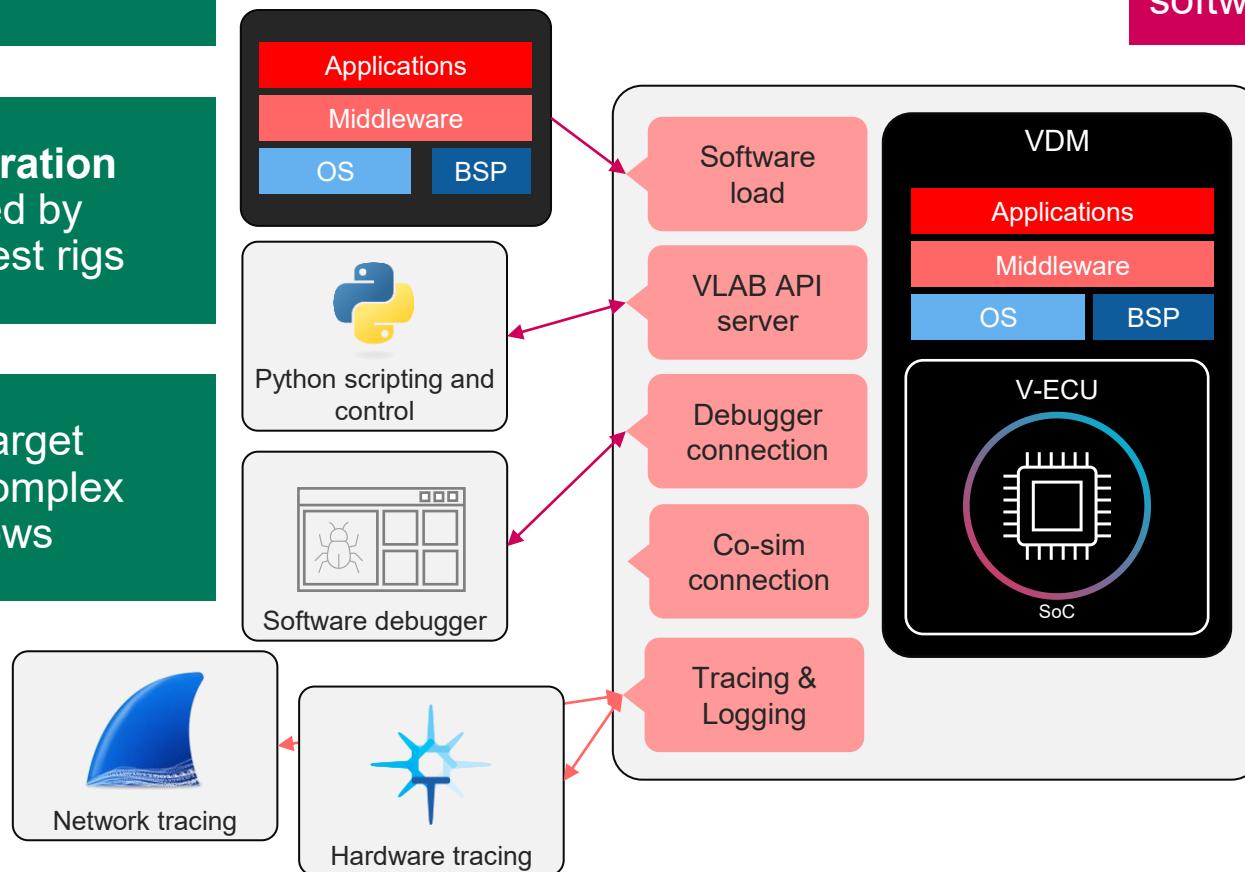

# VLAB™ - Virtualization for Software Development

Complete target-compiled software stack

Virtualization of the target hardware system – ECU, board, system level

Large library of models: cores, SoCs, buses, networks, components

- Industry leading virtualization of embedded hardware for software developers

- **High-performance** hardware simulation (multiple GIPS/GHz)

- Multithreaded and multi-process execution for cores, IP models, and SystemC plugins

- Scalable, on-demand capacity for CD/CI/CT flows

- Access for local and global development teams

- Run on a laptop, desktop, server, or in the cloud

## Ecosystem

Debug using any standard debugger

Connect to system simulators

Embedded and automotive test tools

Integrate 3<sup>rd</sup> party hardware models

Script and automate in Python

Export traces and logs for analysis

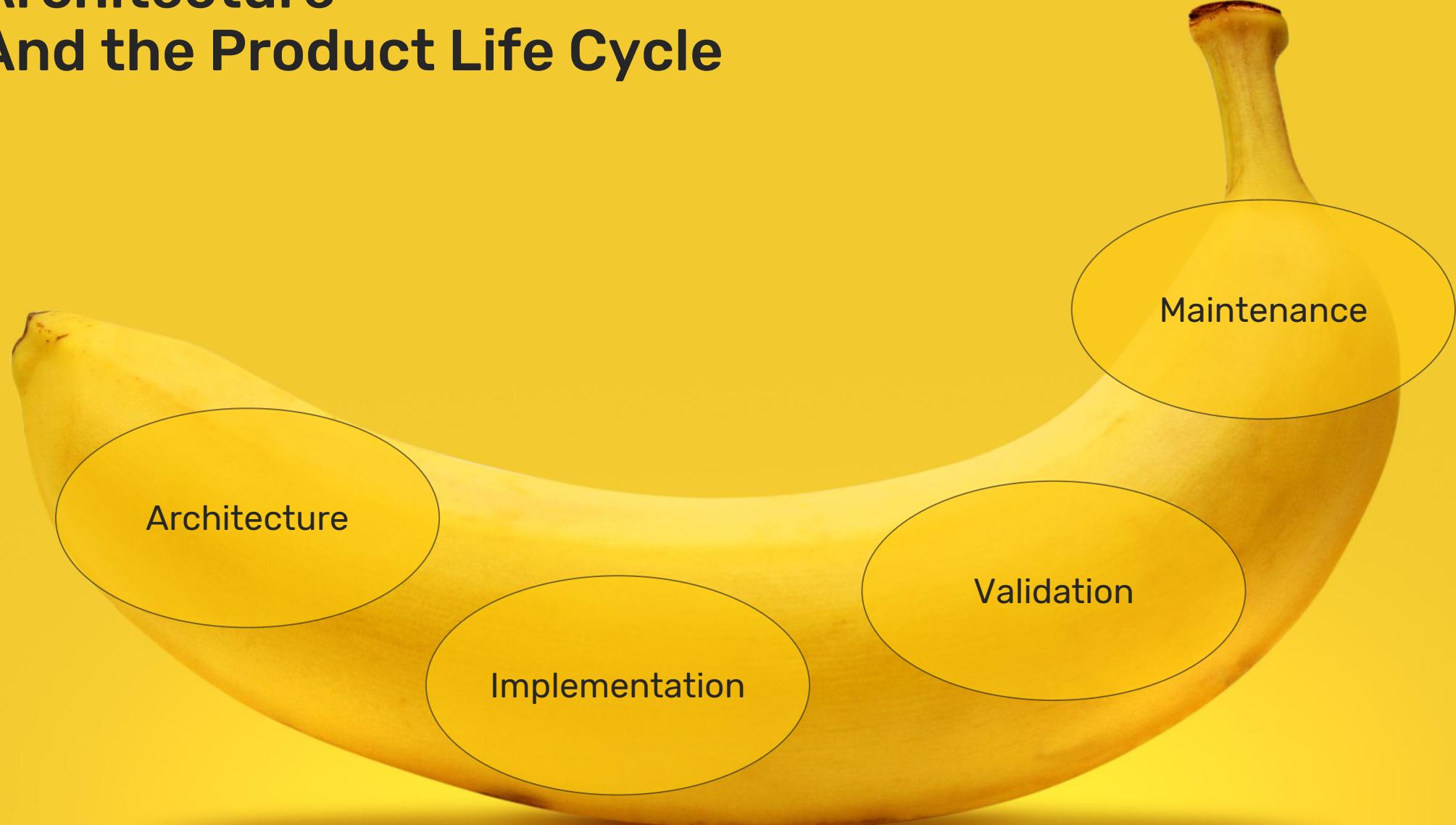

# Architecture – And the Product Life Cycle

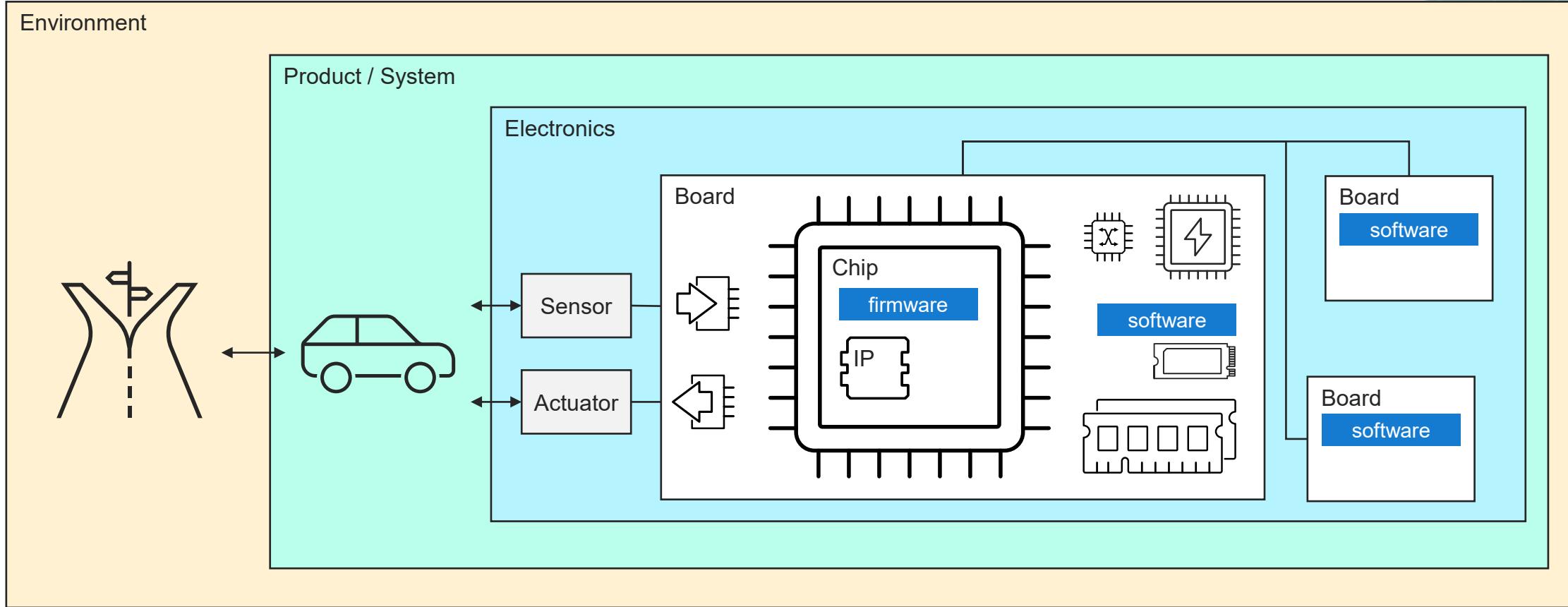

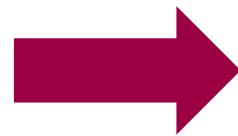

# What is a System? (Featuring Chips & Software)

RAPIDO

2026

Virtual Platforms for System

Architecture, Development, and Test

Dr Jakob Engblom, Cadence, [engblom@cadence.com](mailto:engblom@cadence.com)

cadence®

# Systems Featuring Chips & Software

# Architecting (Something) (With Models)

What are you architecting?

Where are the main risks and unknown?

What is important to model?

What is **not** important to model?

What is under your control?

What external inputs, factors, behaviors must be considered?

The **model** should be faster and easier to change than an actual **implementation** for modeling to make sense

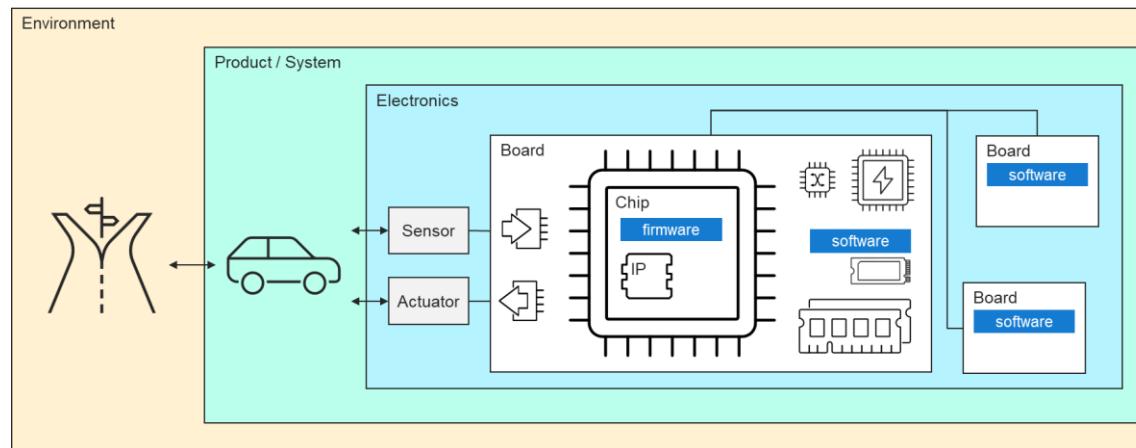

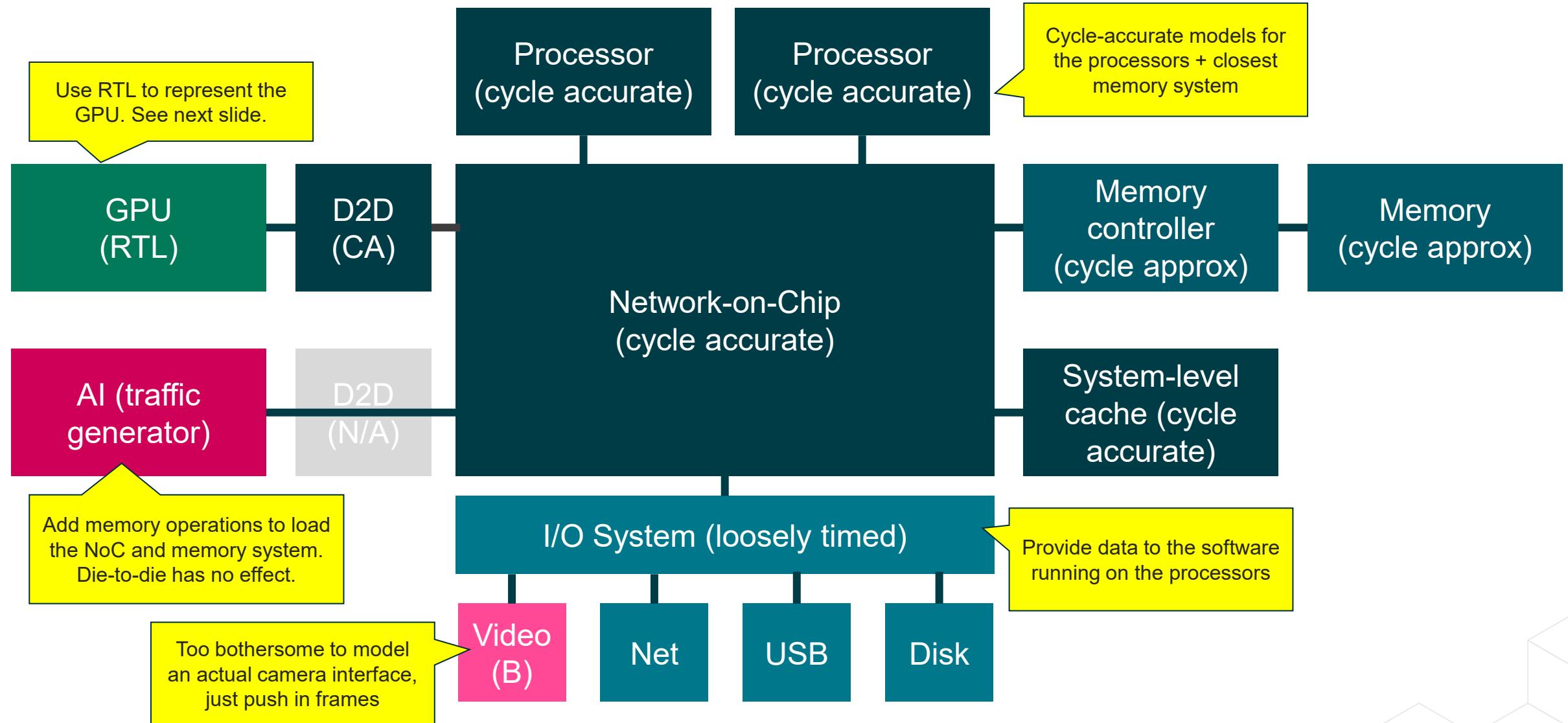

# Architecting a Chip (Generic SoC for Automotive, Mobile, etc.)

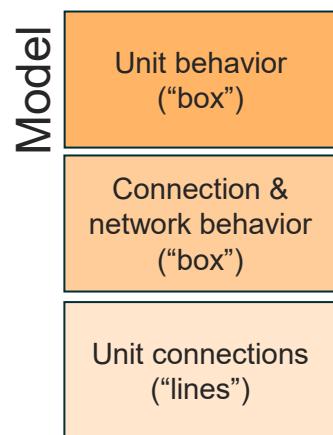

# Modeling Hardware Units and Interconnects

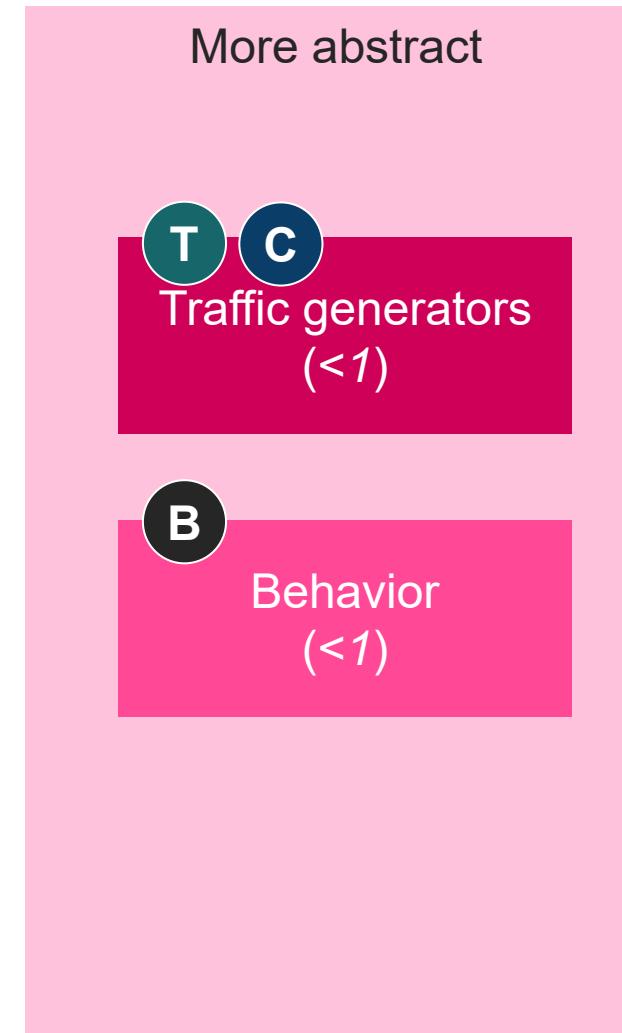

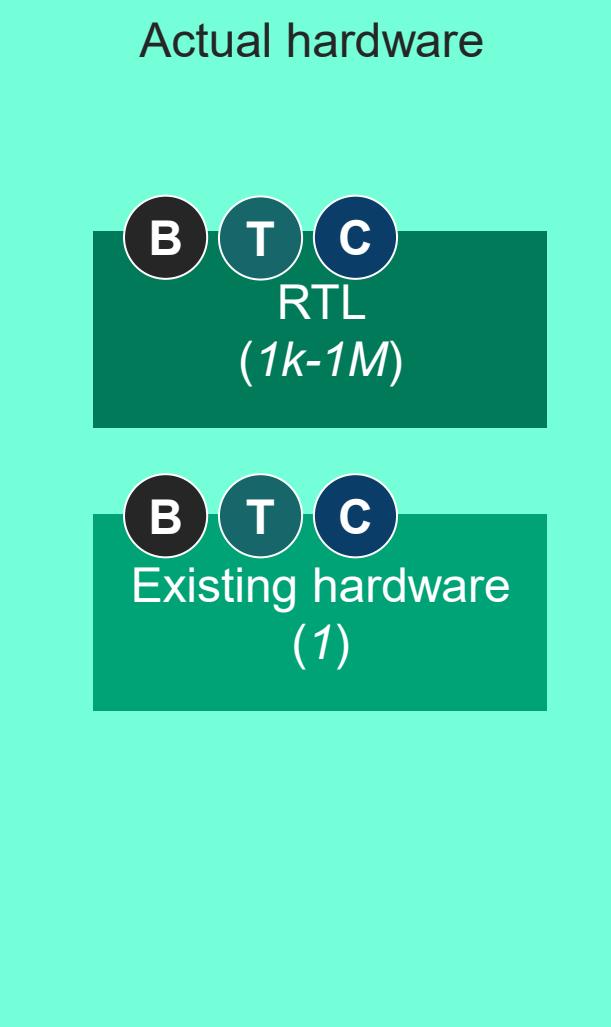

- B** Behavior / functionality

- T** Timing

- C** Contention

Classic virtual prototyping / virtual platforms

**B** **T** **C**

Cycle-accurate (100k)

**B** **T** **C**

Approximately-timed (10k)

**B**

Loosely timed (10)

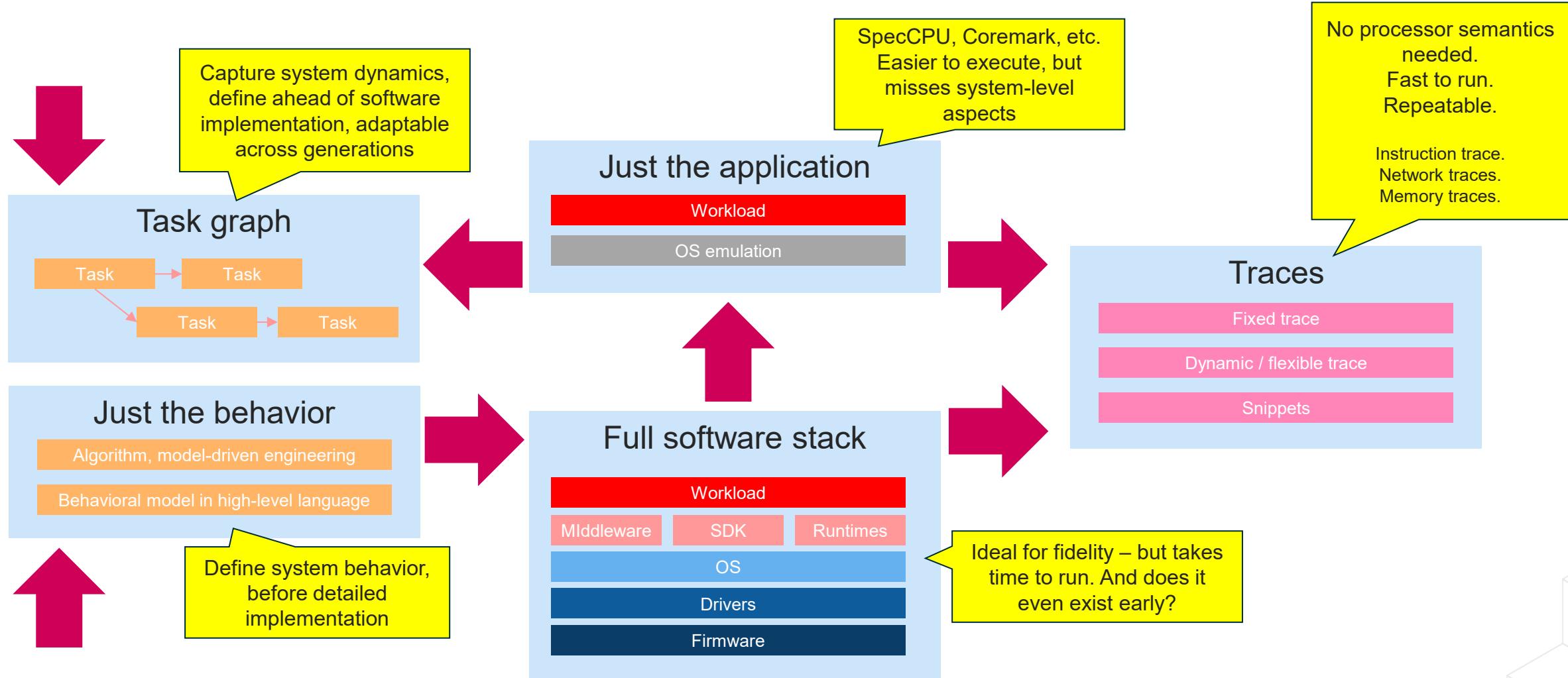

# Modeling Software

# Attention! Feedback Loops!

## Examples

### Power management

- Application *is* a control loop

- Throttle on overheating

- Speed up when cool

- Speed up when plugged in

- ...

### Games

- Measure achieved frame rate

- Adjust quality settings to reach frame rate

- Measure input latencies, adjust handling

### Streaming & video

- Adjust video quality based on network bandwidth

- Prioritize traffic

### Interrupt timing

- Change to software timing

- Changes when OS schedules tasks

- Divergent behavior

### JIT compilers

- Measures execution time using performance counters

- Decides what to compile dynamically

Fixed traces (often) fail to capture feedback loops in the system behavior and can be **directly misleading**

# Example: For a Processor Core Architect

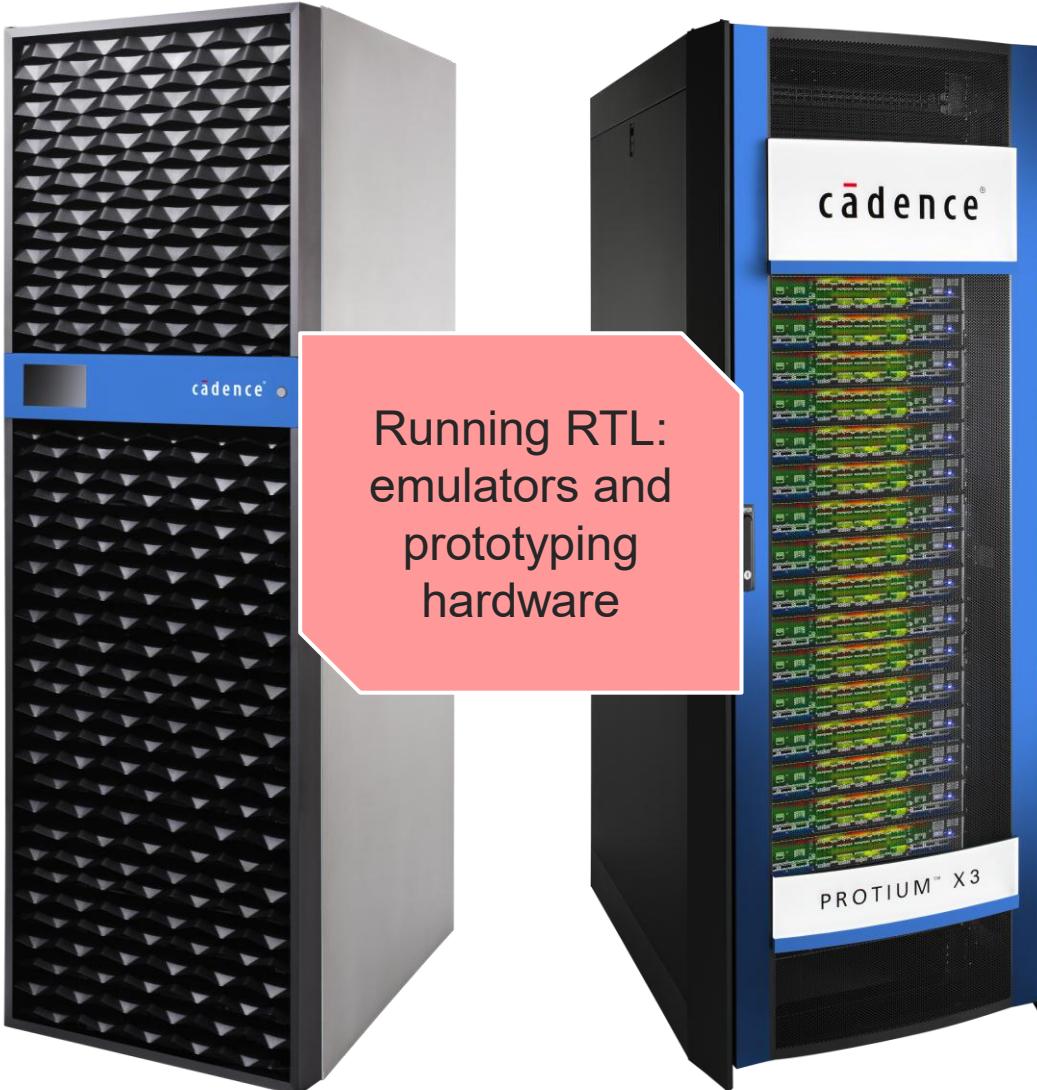

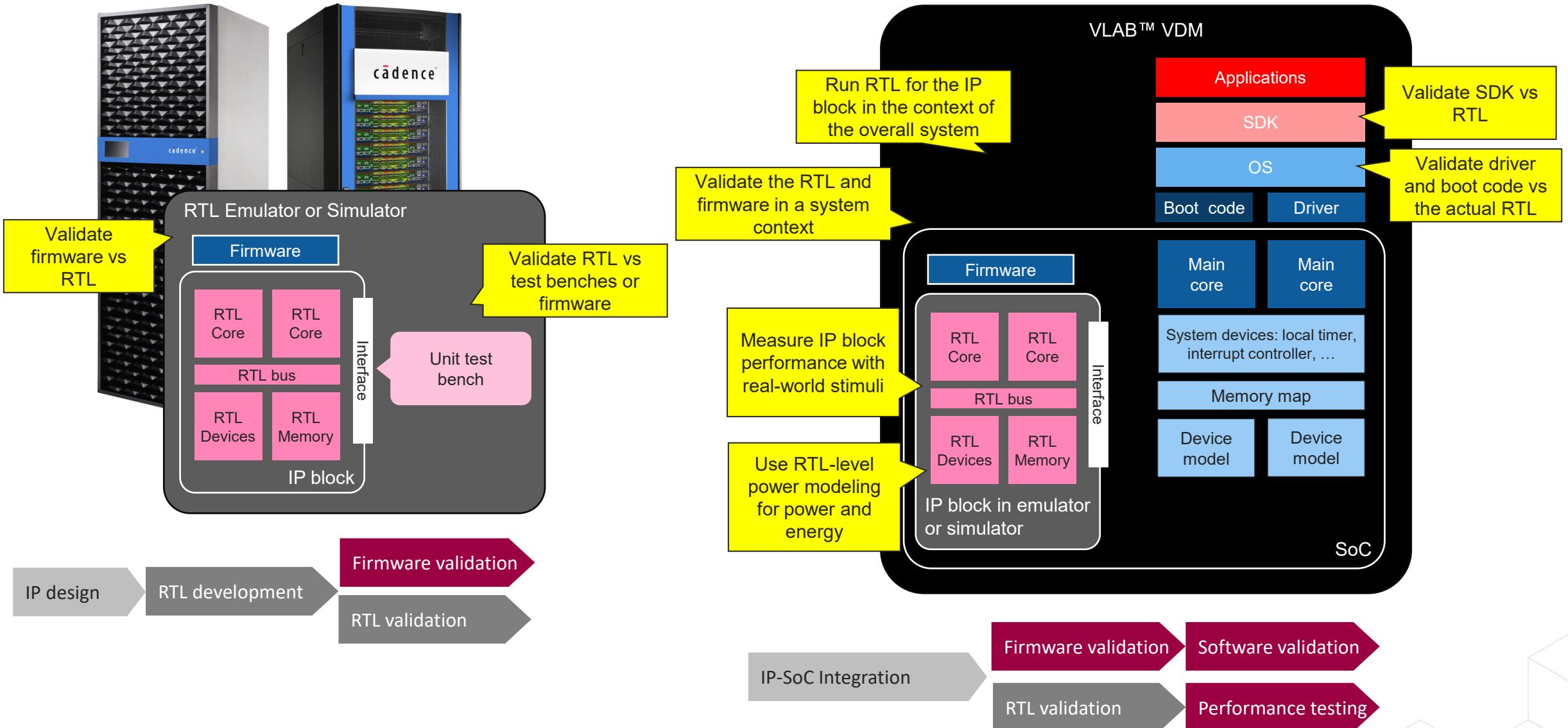

# Using the RTL Implementation as Model

- Architecting a **chip**

- Buying **components**

- = the components are done

- Architecture = configuration & interactions

- How many processor cores?

- How many GPU slices?

- Clock speed?

- Power budget?

- Bandwidth of the interconnect?

- Structure of the interconnect?

- Running pieces as RTL makes sense

- “Fast” with emulators and prototypes

- Modeling someone else’s design is *hard*

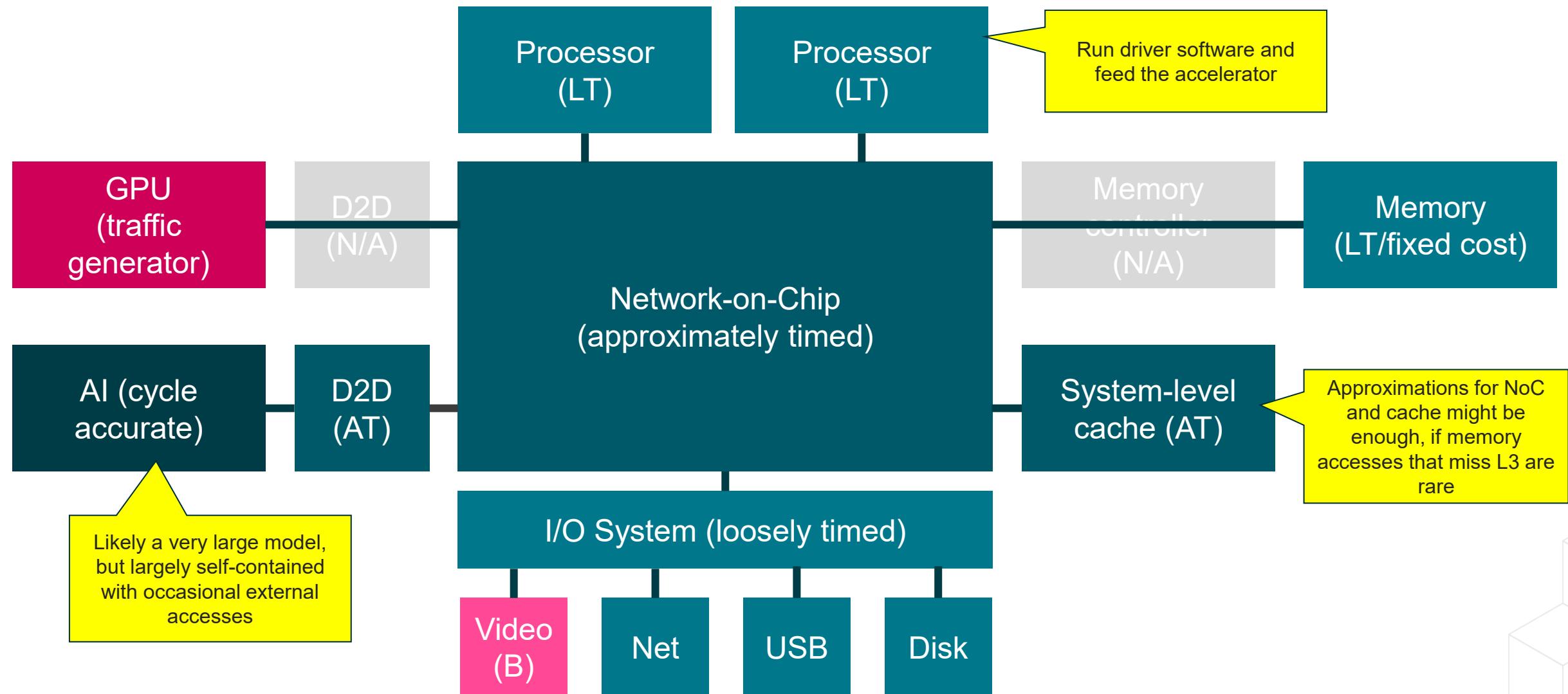

# Example: For an AI Accelerator Architect

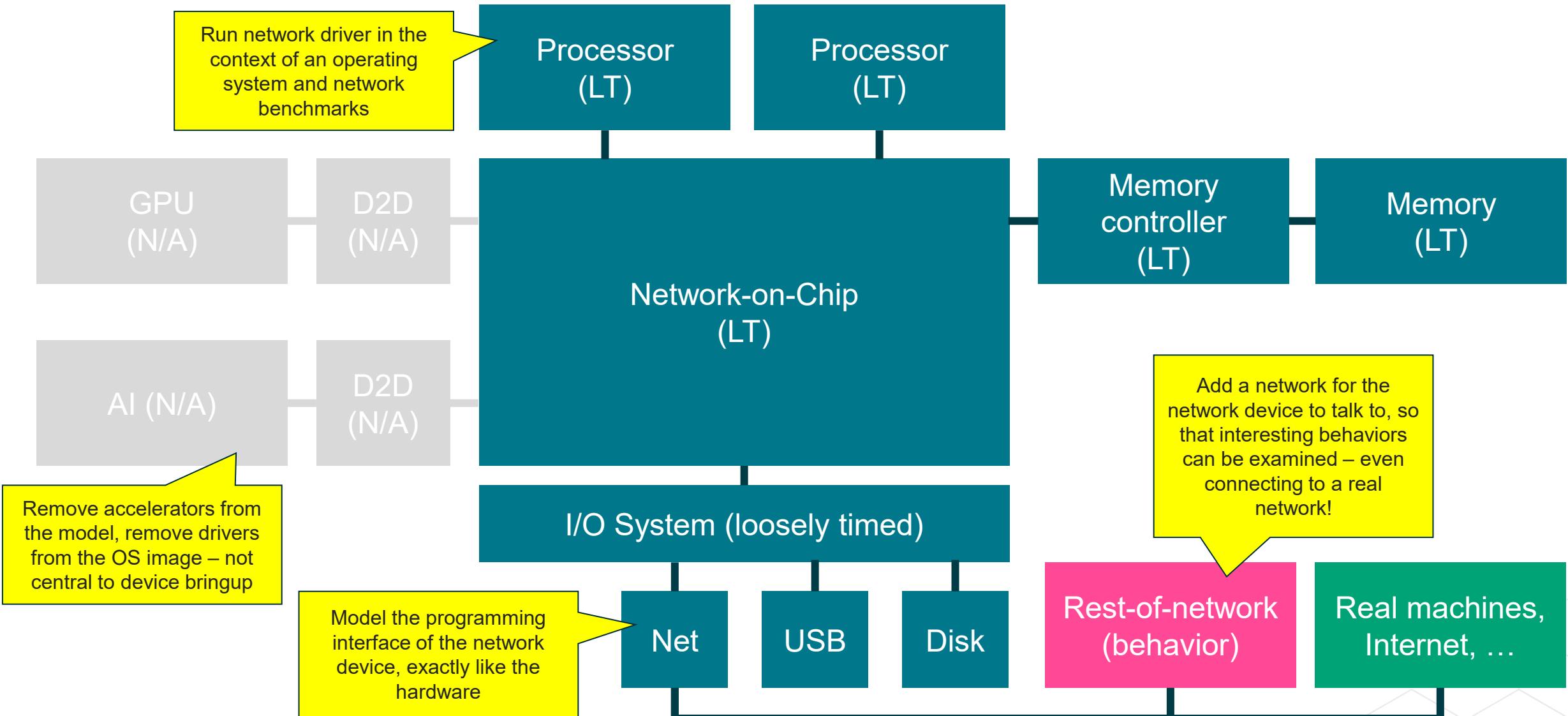

# Example: For a Device Interface Designer / Architect

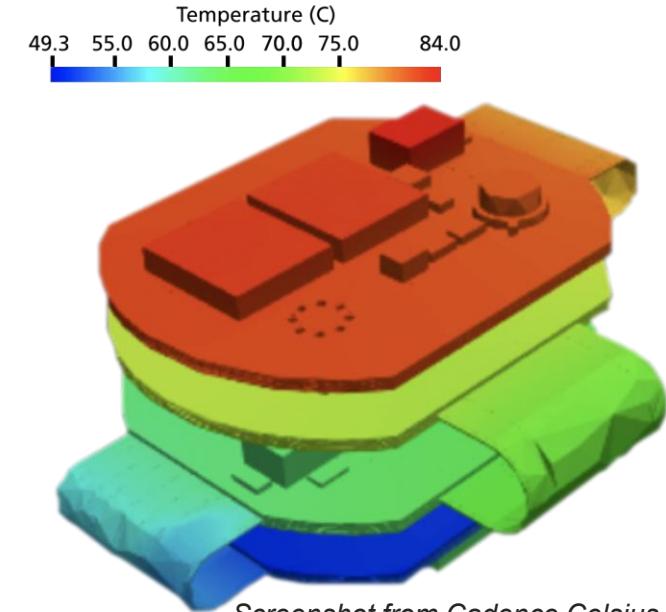

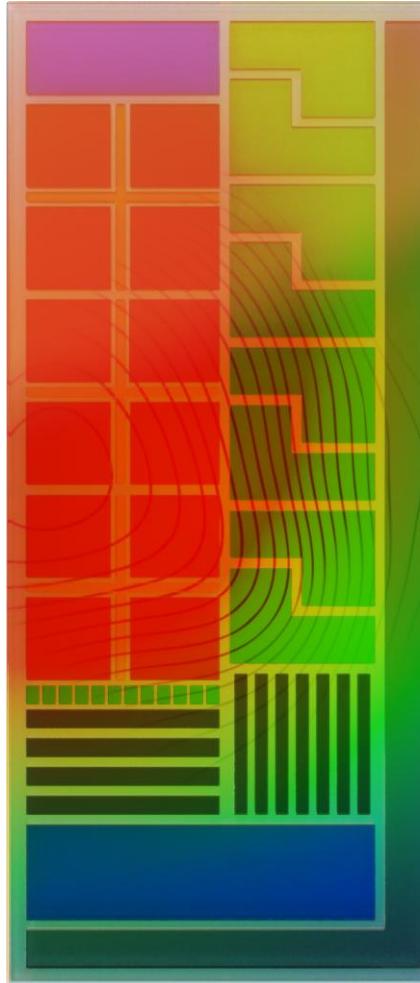

# Modeling Power, Energy, Thermals

- Power is “easy”

- Power state, clock speed, voltage, ...

- Essentially, functional aspects that are set by software and firmware

- Energy is trickier

- $\text{Energy} = \text{Power} * \text{Time}$

- Requires a precise timing model

- Thermals are even trickier

- Requires a good energy model

- Energy to heat conversion model

- Geography of the chip

- Thermal properties of materials

- Heat propagation and cooling

- = complex physics simulation

*Screenshot from Cadence Celsius*

*Analysis by Cadence Celsius*

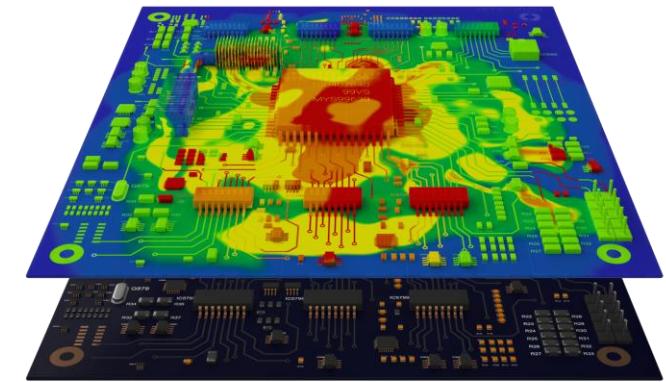

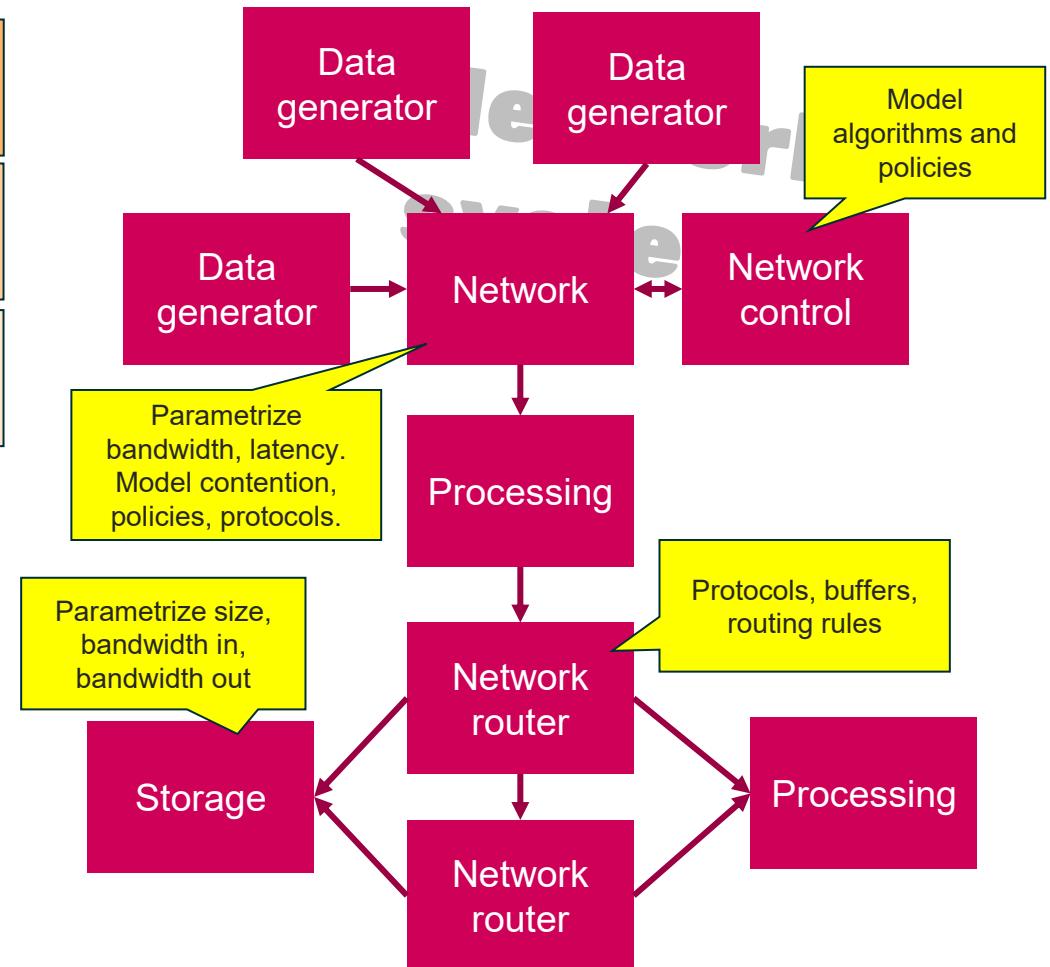

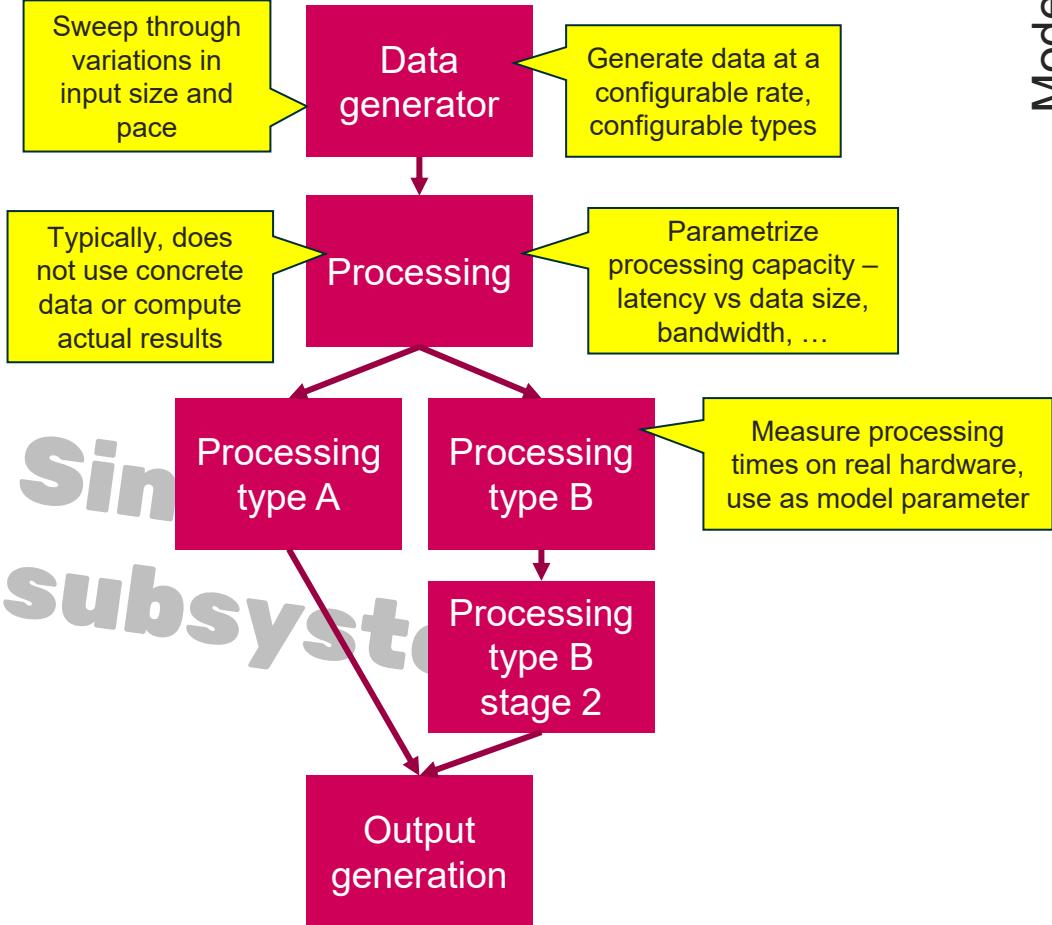

# More Abstract Models – “Boxes and Lines” – Examples

Abstract models can give surprisingly accurate results – turn Excel sheet guesses into executable model

Very suitable for complete system models beyond a single IP or chip

# Example Higher-Level Model

VisualSim model of a Five Node Network

**MIRABILIS**

design

Source : VisualSim Architect

Used with permission of Mirabilis Design

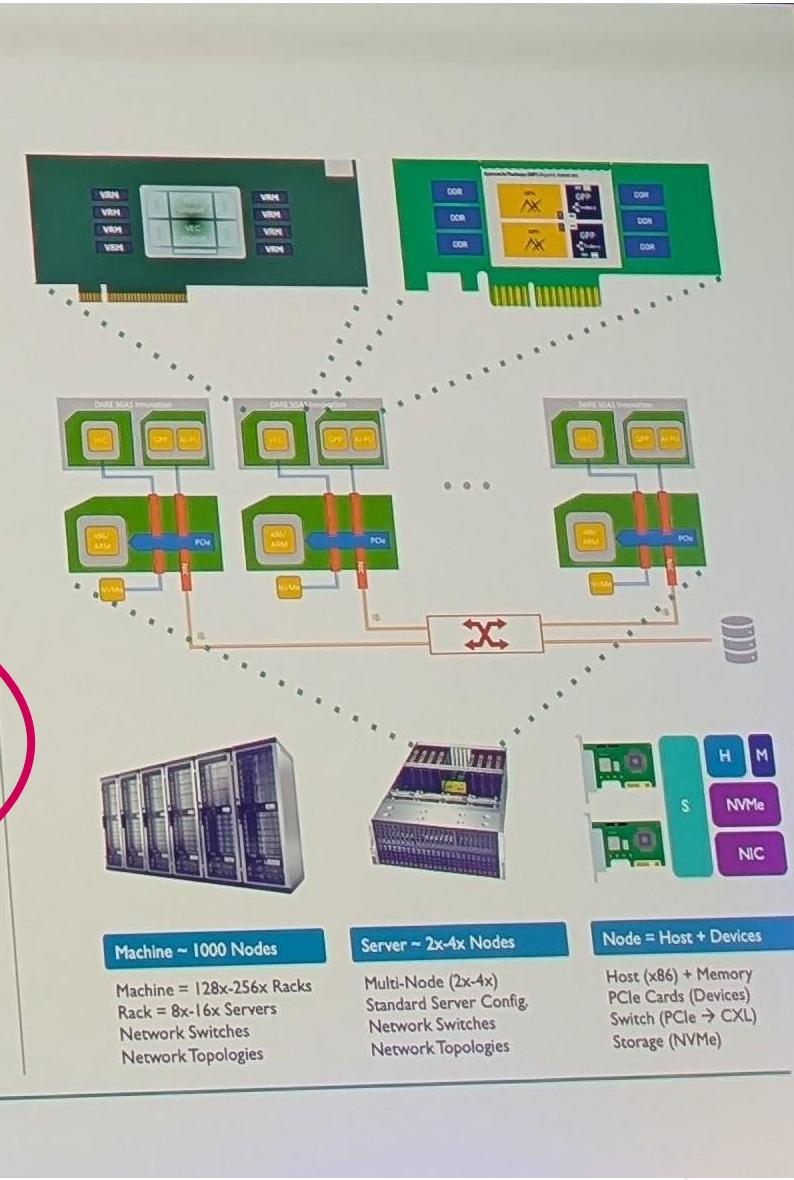

# Example: From DARE Project (HiPEAC RISC-V Workshop)

## INT TA objectives

- **DARE Devices:** Realisation of a set of DARE devices through physical design of chiplets, design of substrate and silicon interposer and SiPs for chiplet integration, PCB design and fabrication, and bring-up and characterisation of boards

- **Physical Prototype:** Realisation of a multi-node machine with each node housing a standard x86 host and multiple DARE devices (integrated in the form of PCIe cards)

- **Virtual Prototype:** Realisation of a virtual twin of a multi-node (~100x-1000x) machine built as a PDES (parallel discrete event simulator) multi-fidelity model to integrate models of DARE devices at an appropriate abstraction and with the required interfaces (e.g., PCIe, CXL over PCIe/UCLe)

*The form factor of the devices, the physical prototype and the virtual prototype in the diagrams are for representative purposes only; to be finalized in the System Architecture Definition phase.*

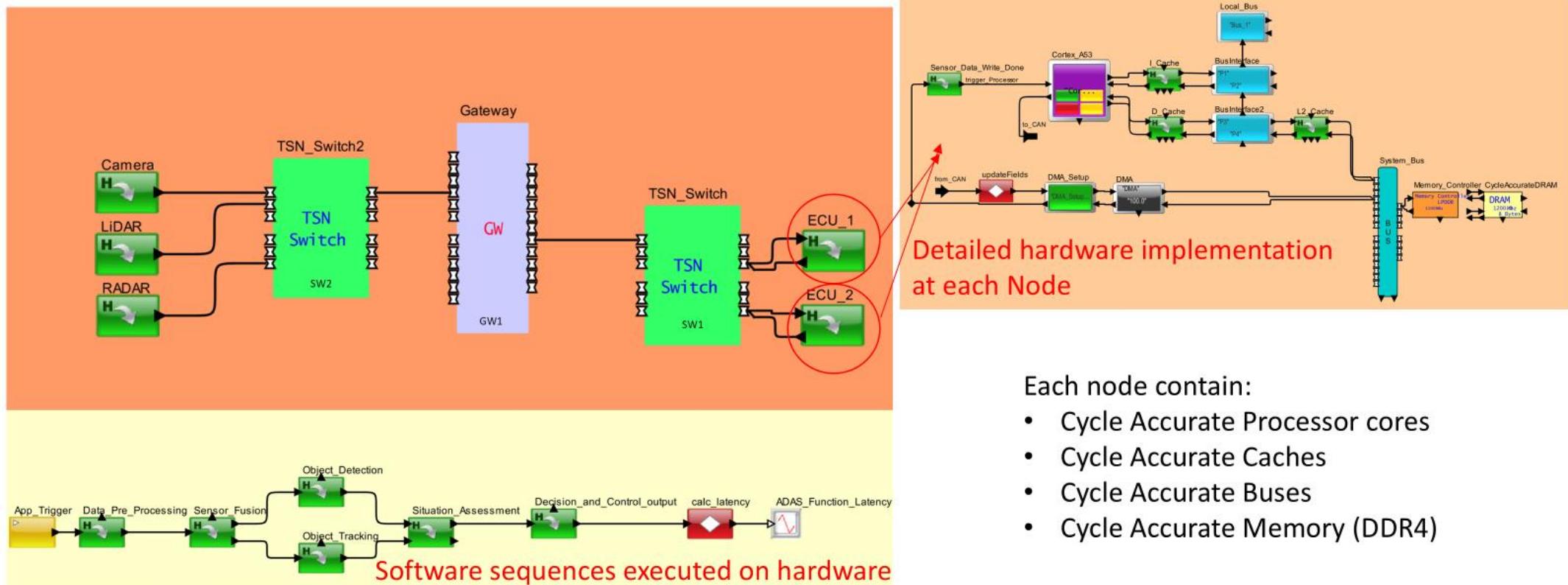

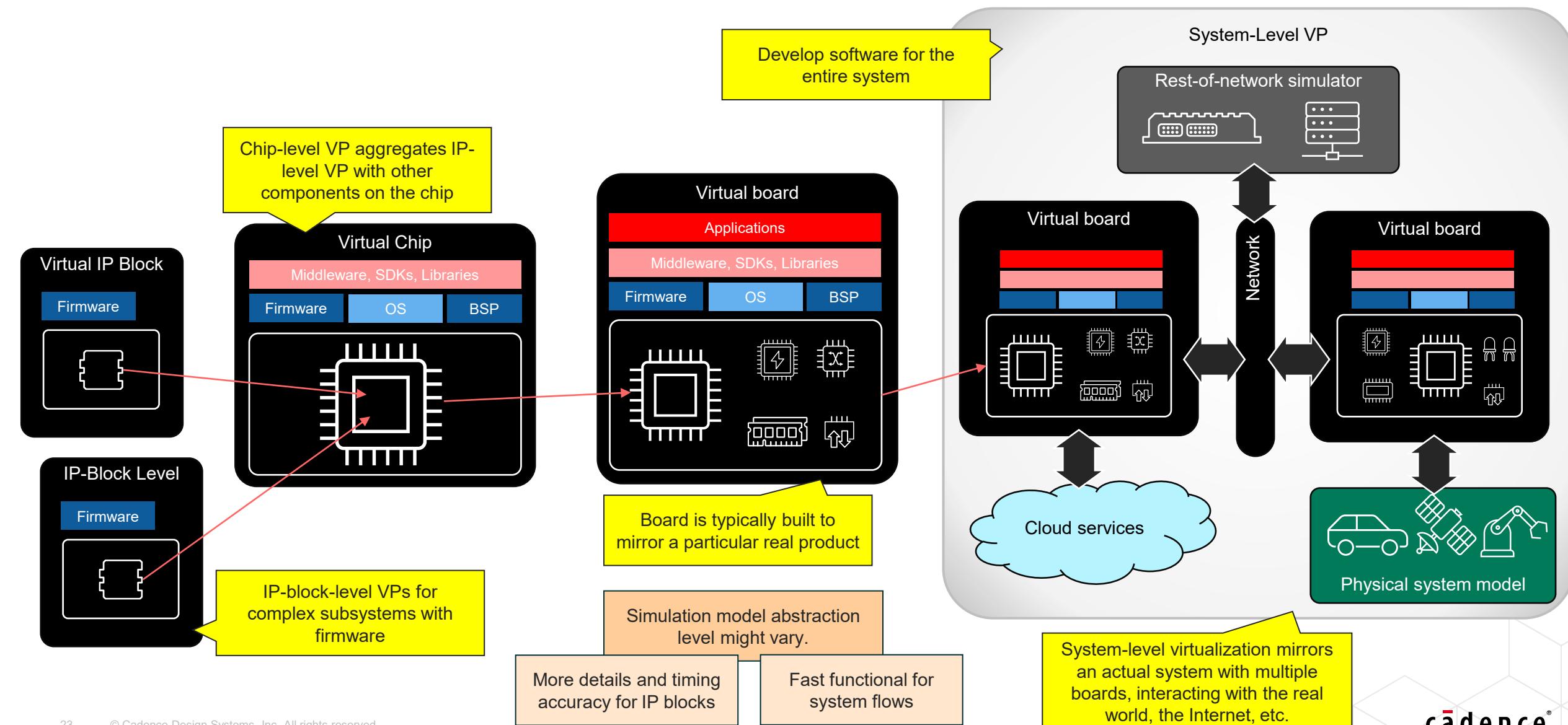

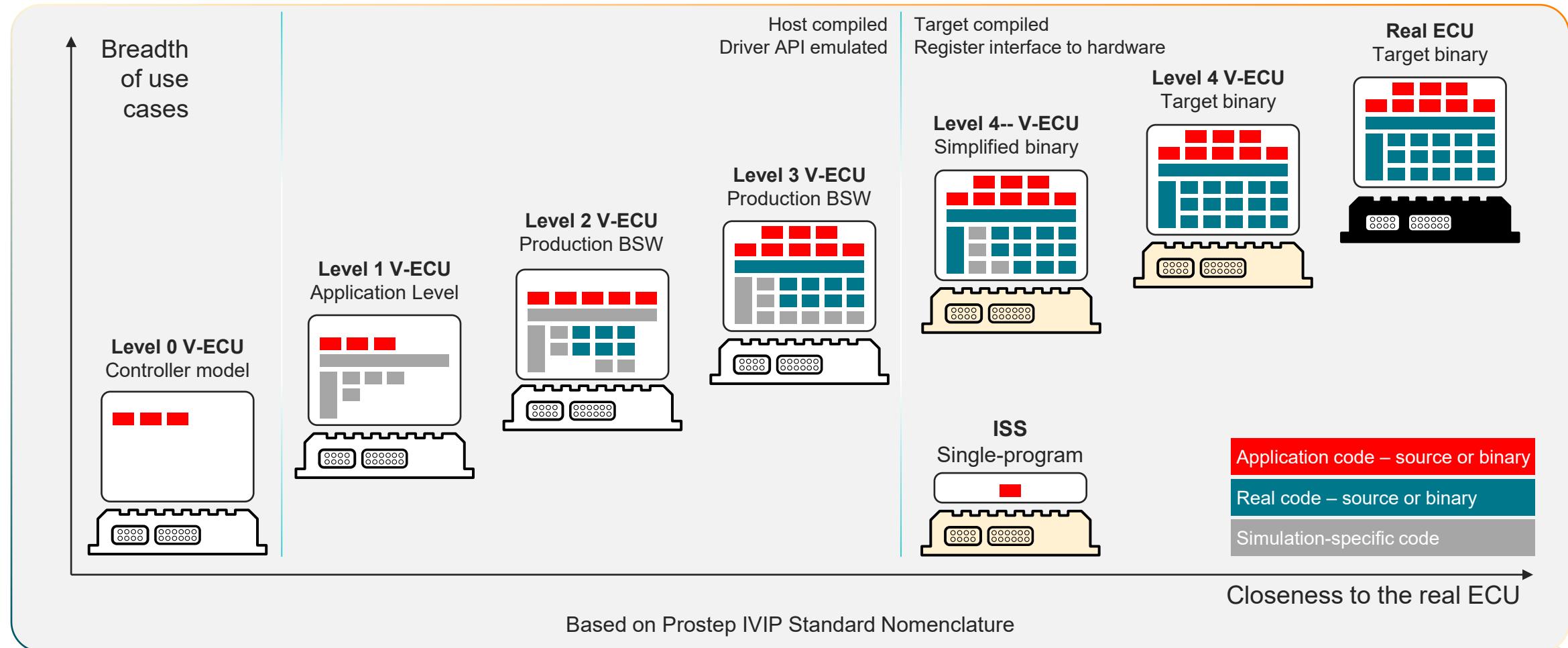

# Virtual Platforms – From IP to System, Developing Software

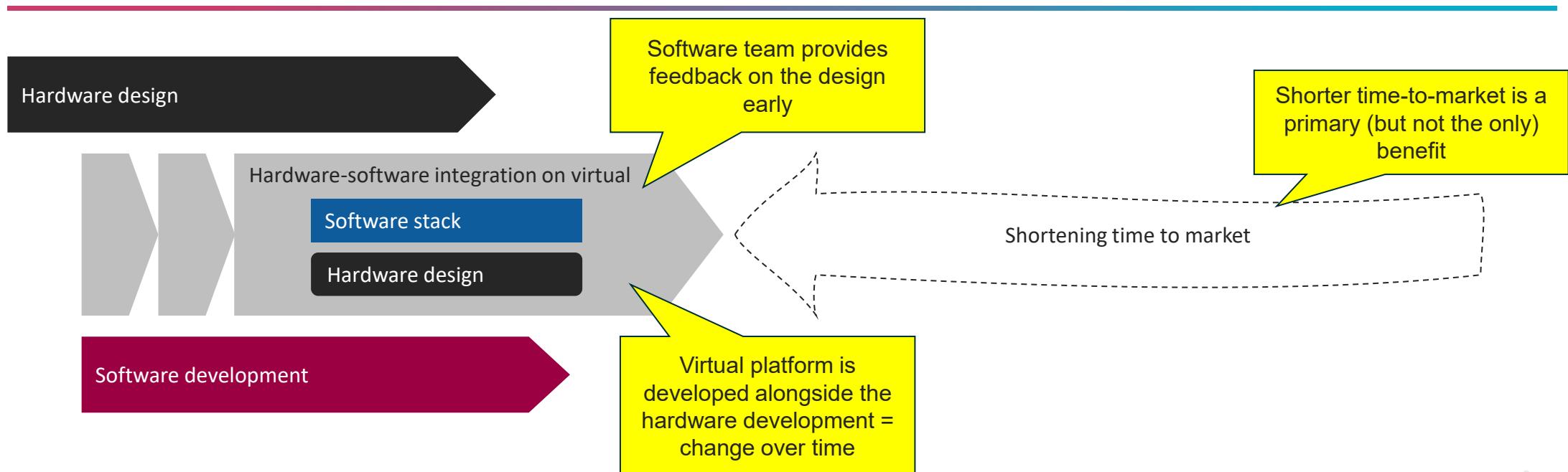

# Using Models at the Implementation Stage: Shift Left

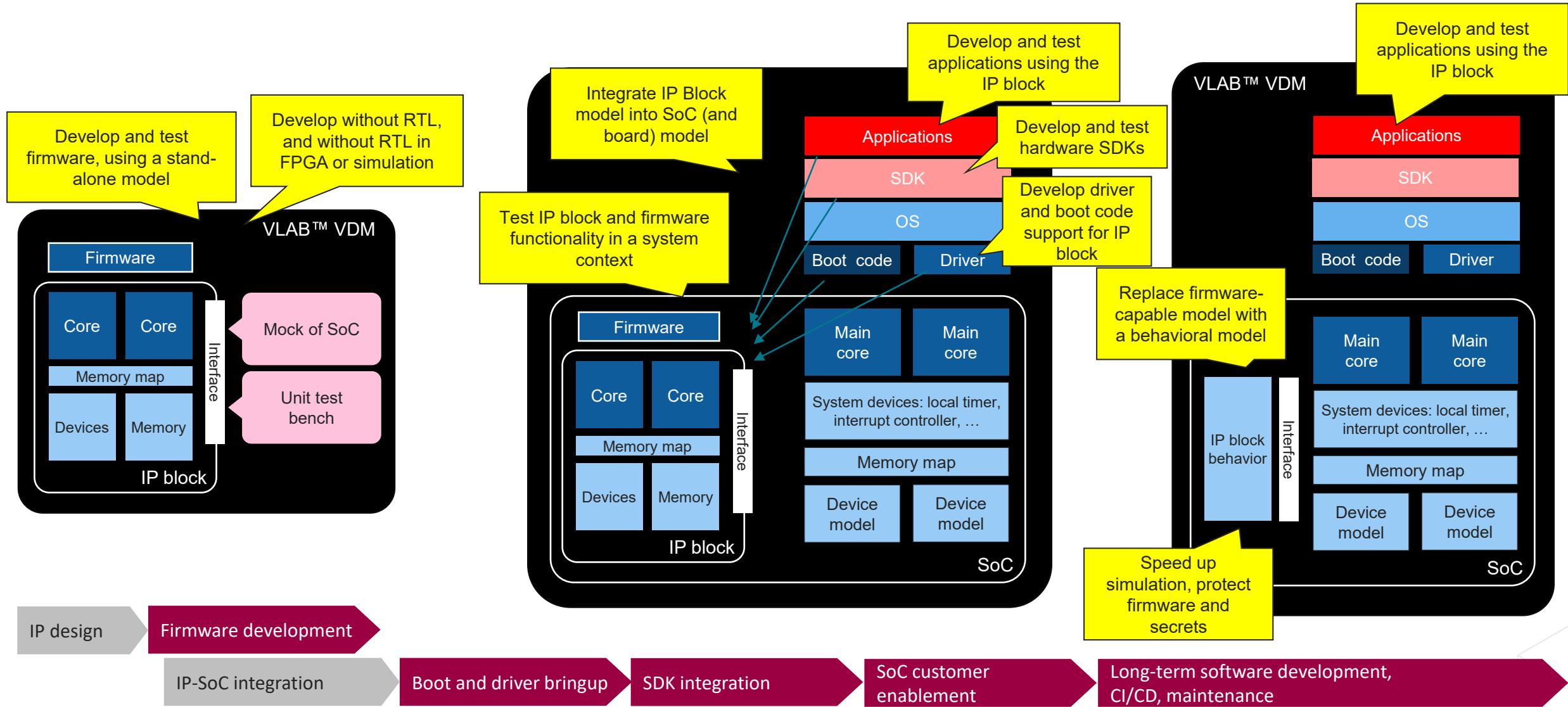

# IP Block Development: Software on VP

# Pre- or Post-Silicon: Free Developers from Hardware Limitations

**Unlimited access to targets for testing** - use any PC, server, or cloud VM to run tests

**Apply any test configuration on-demand** – not limited by availability of physical test rigs

**Load software** to the target system instantly – no complex flashing or download flows

**Automate and script any action** —the simulator has perfect insight and control, control over time, react to hardware and software events

**Debug better than hardware** – powerful breakpoints, complete system inspection, debug across all cores, ...

**Trace and log everything** – software, hardware, networks, ...

**Inject faults**, force boundary conditions, ...

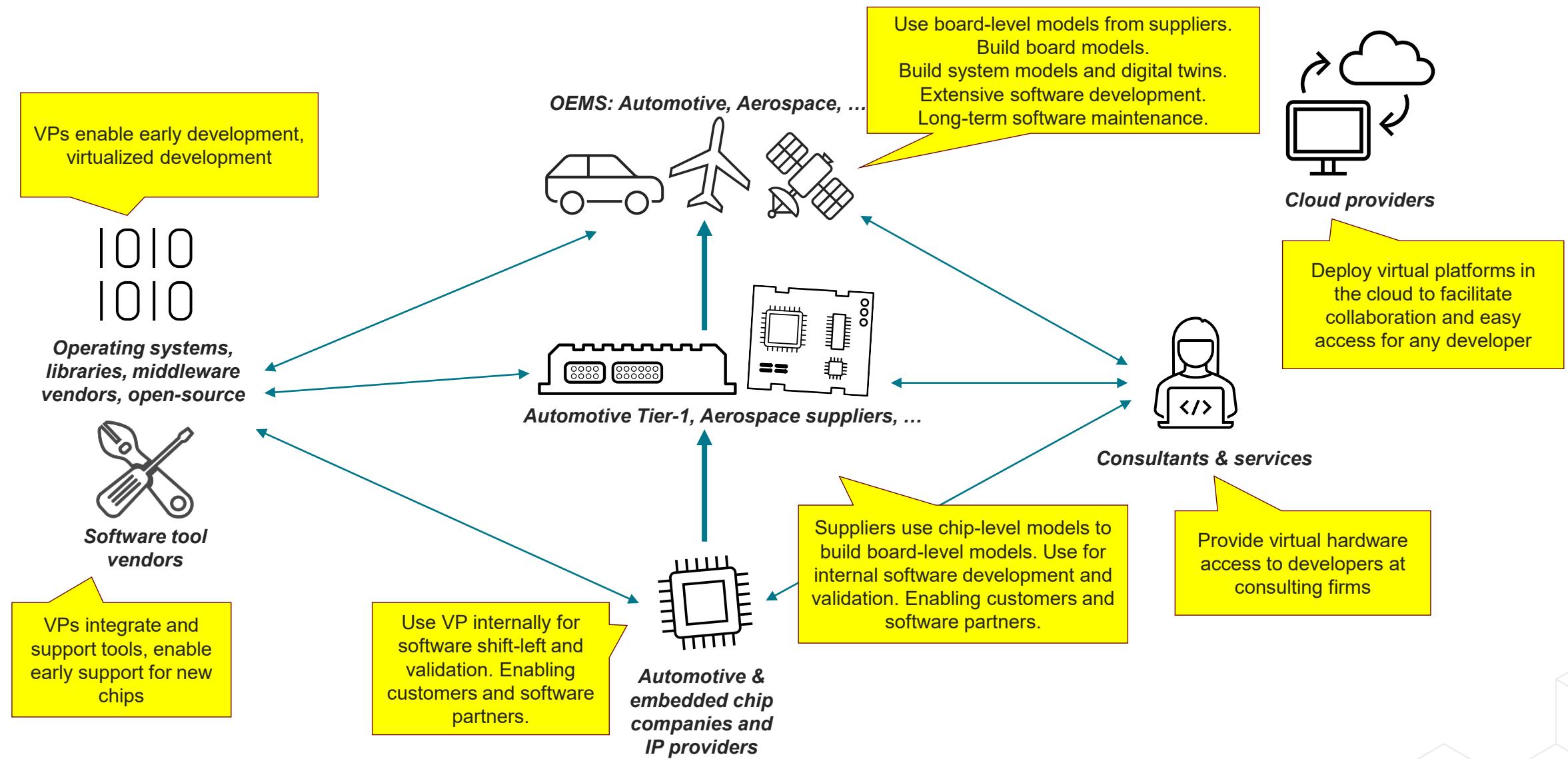

# Virtual Platforms as an Ecosystem Collaboration Tool

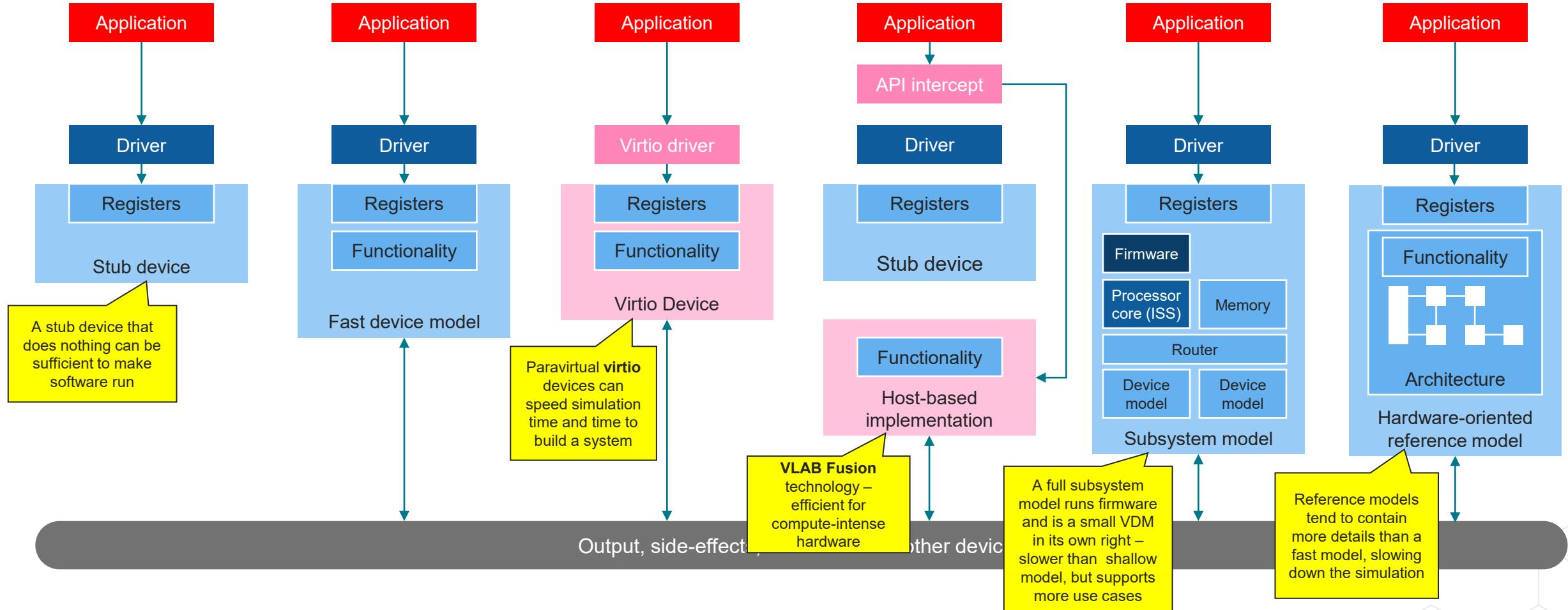

# Fast Functional Model Variants – Optimize for Performance

# Automotive Variants Simpler Than Traditional Virtual Platforms

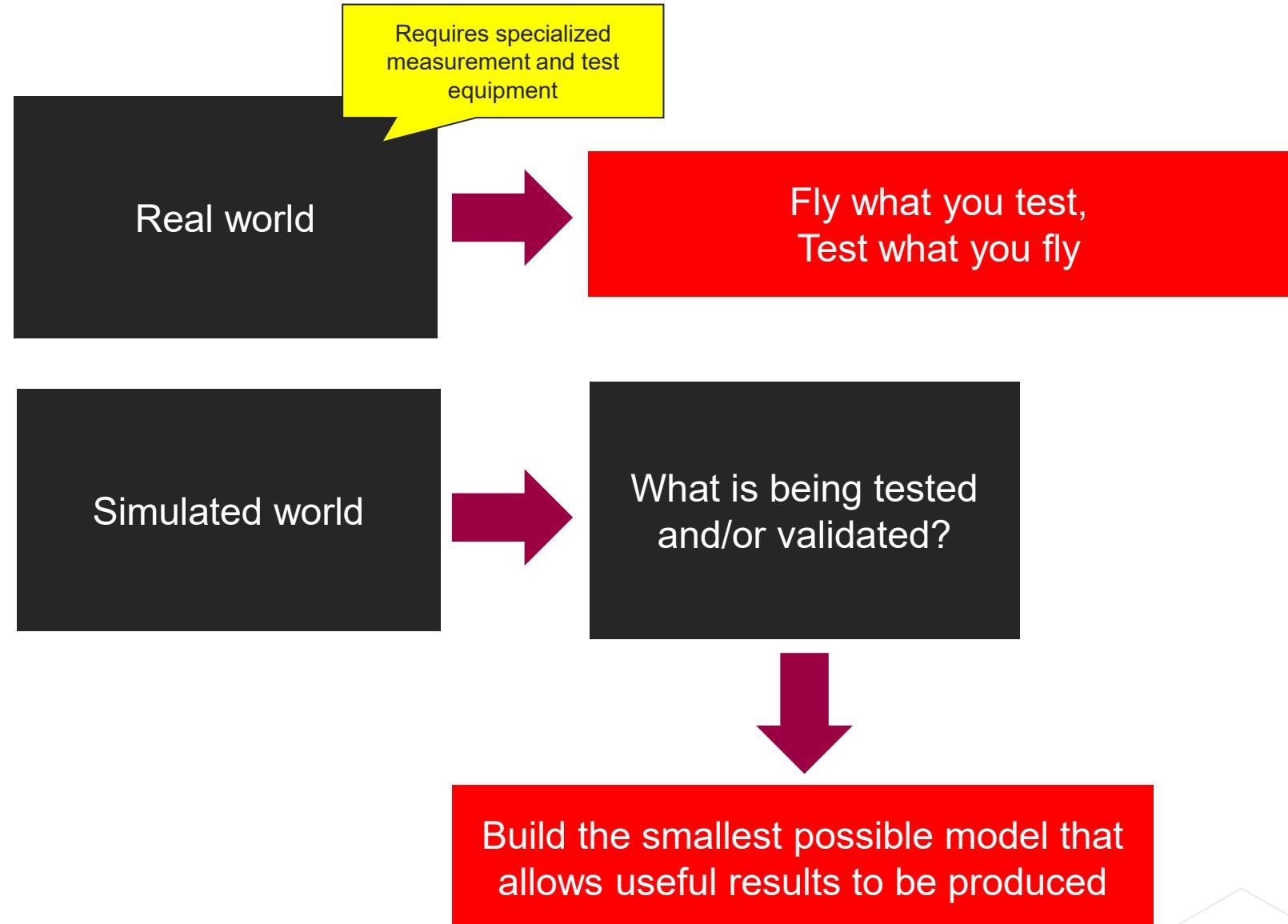

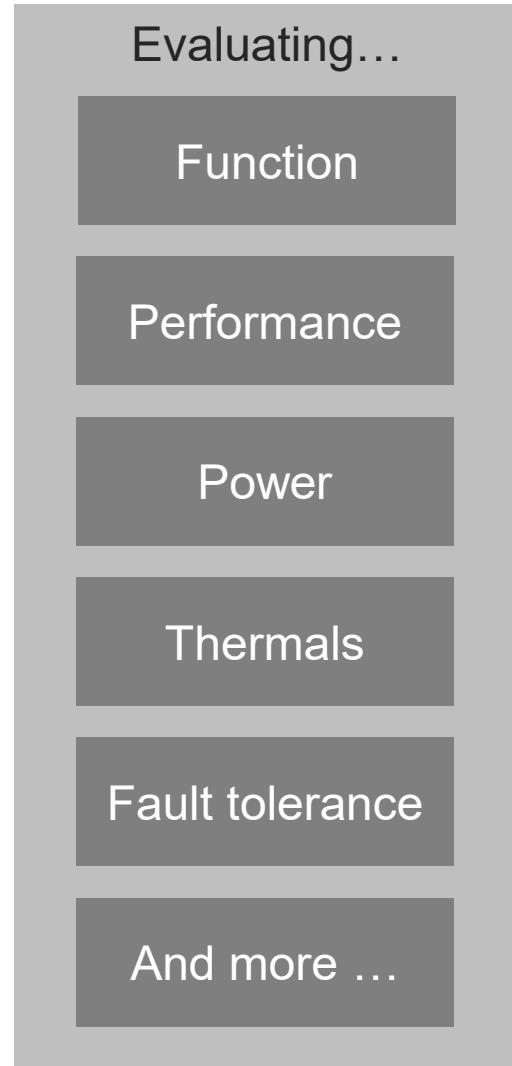

# Validation – Does the System Work Right in Practice?

# Example: IP Block Development: Validation of the RTL

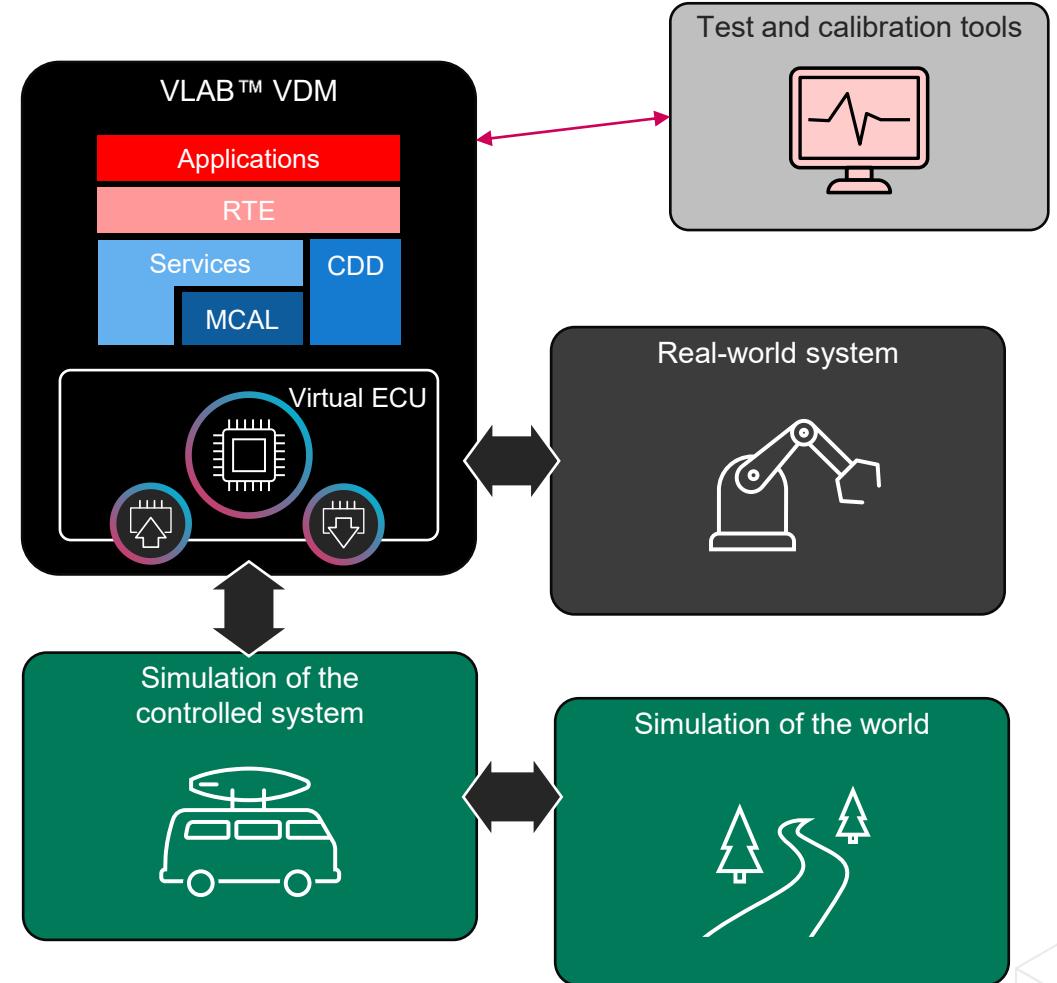

# Virtual Hardware-in-the-Loop Testing

- Hardware-in-the-Loop is the “gold standard” for software testing

- ECU or network of ECUs

- Connected to physical simulation setups

- *(whole ecosystem of solutions for this)*

- Replicate with virtual platforms for virtual testing

- Real software stack

- Simulation setup matching the real world

- Closed-loop simulation including real-world behavior

- Real systems attached to real-time sim

- Attach test and calibration tools to manage tests

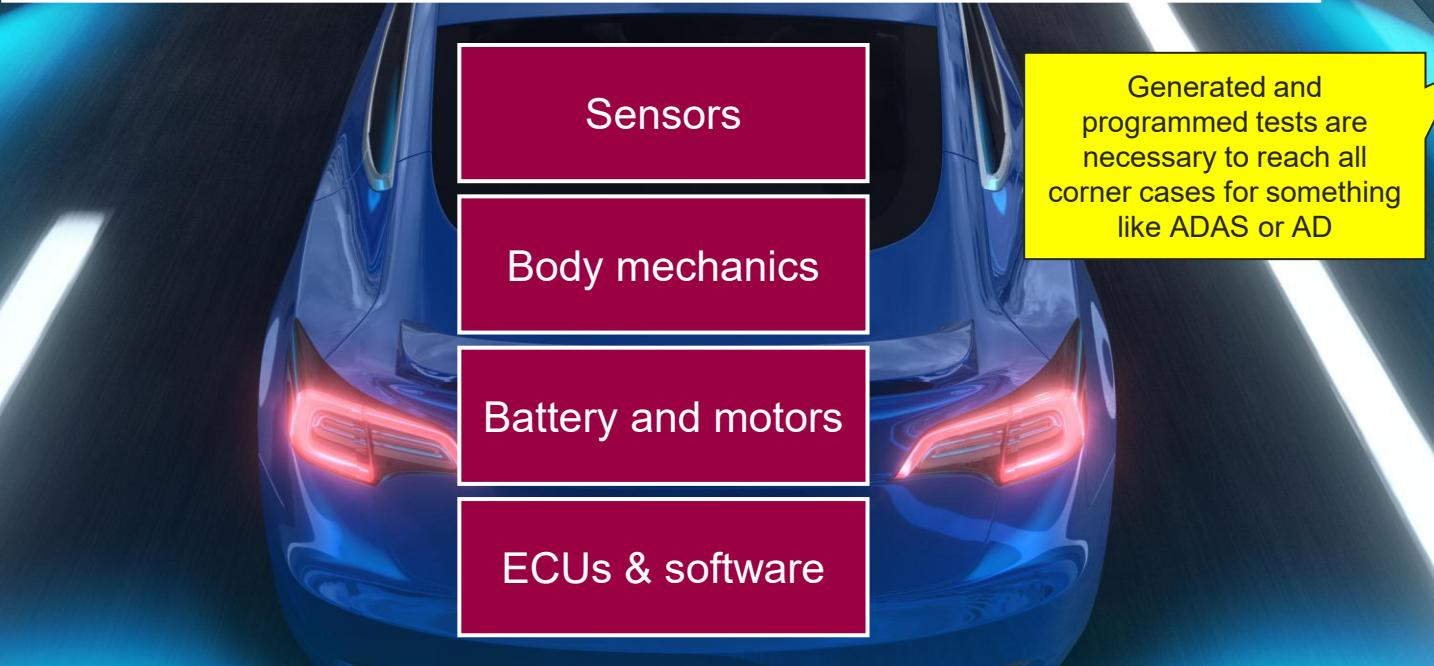

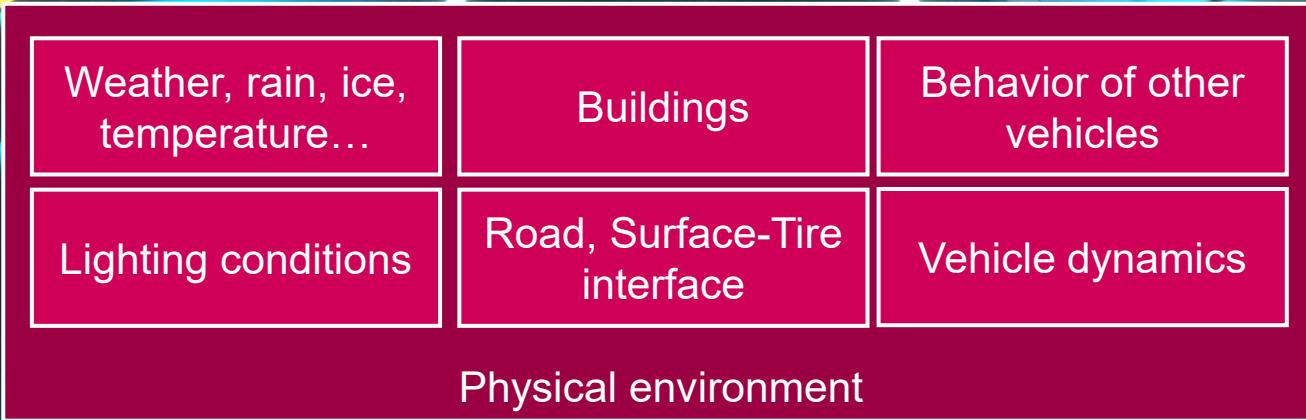

# Validating Automotive Systems

Record & replay real-world tests

Programmed test scenarios

Randomly generated test scenarios

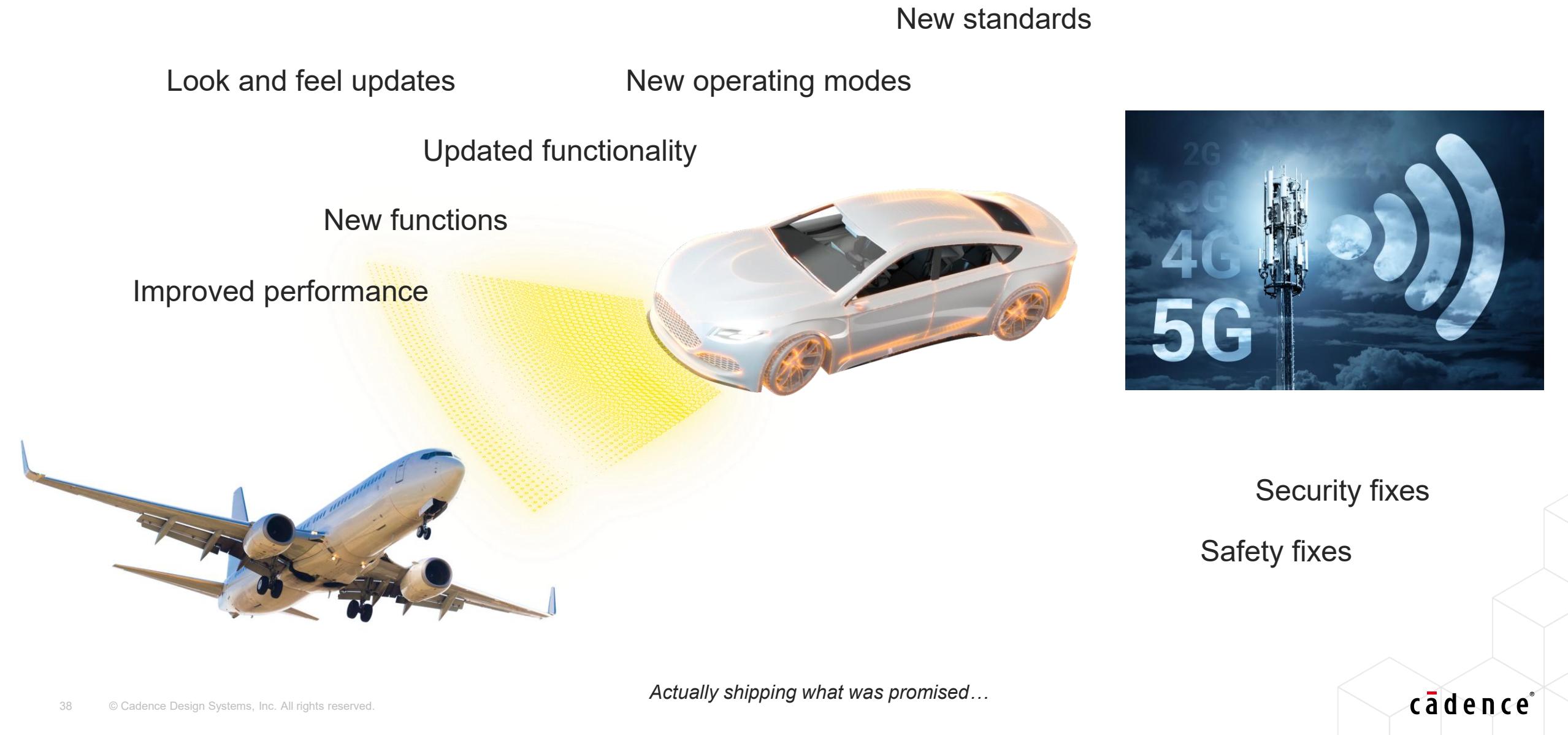

# Deployed Systems Still Require Software Updates

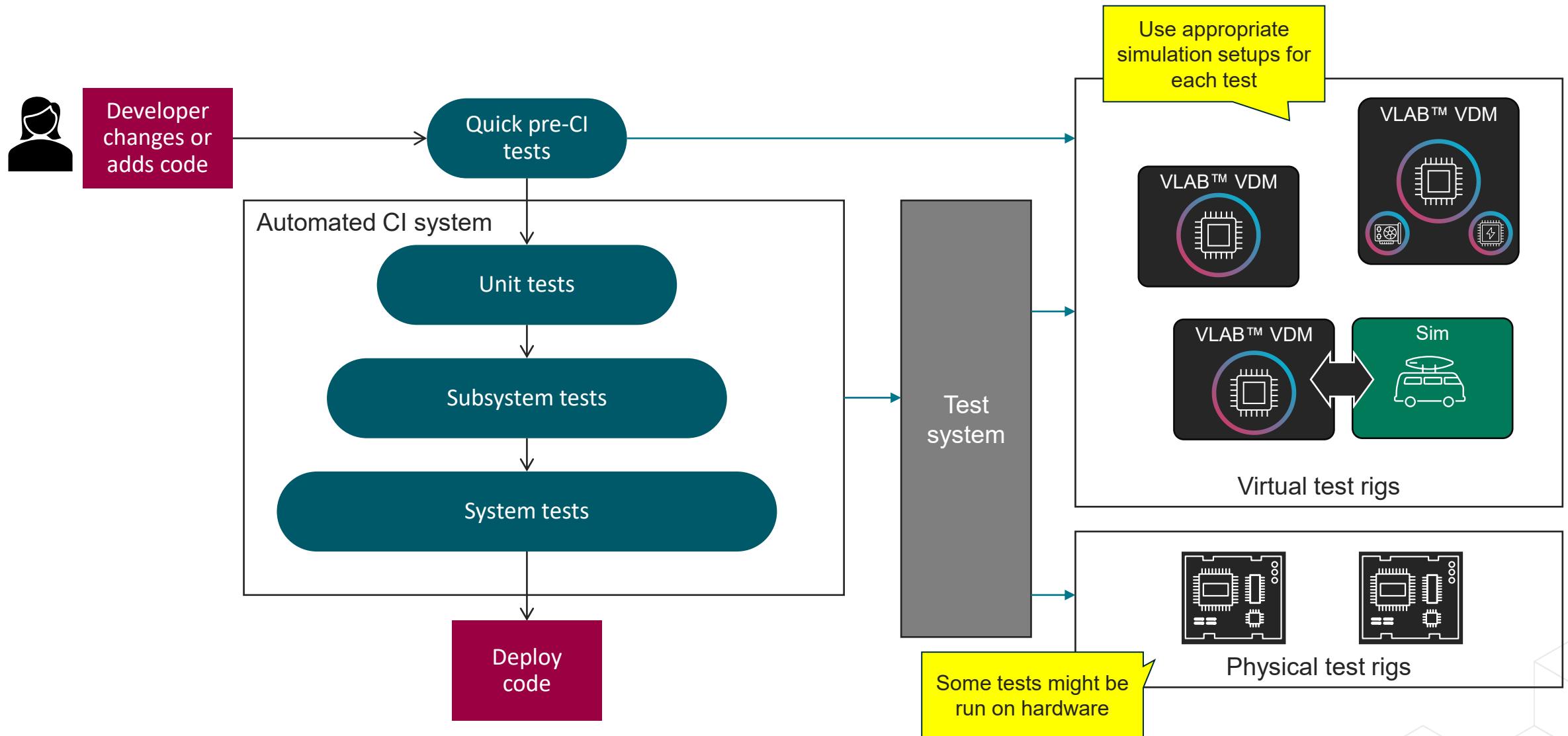

# Continuous Integration and Deployment

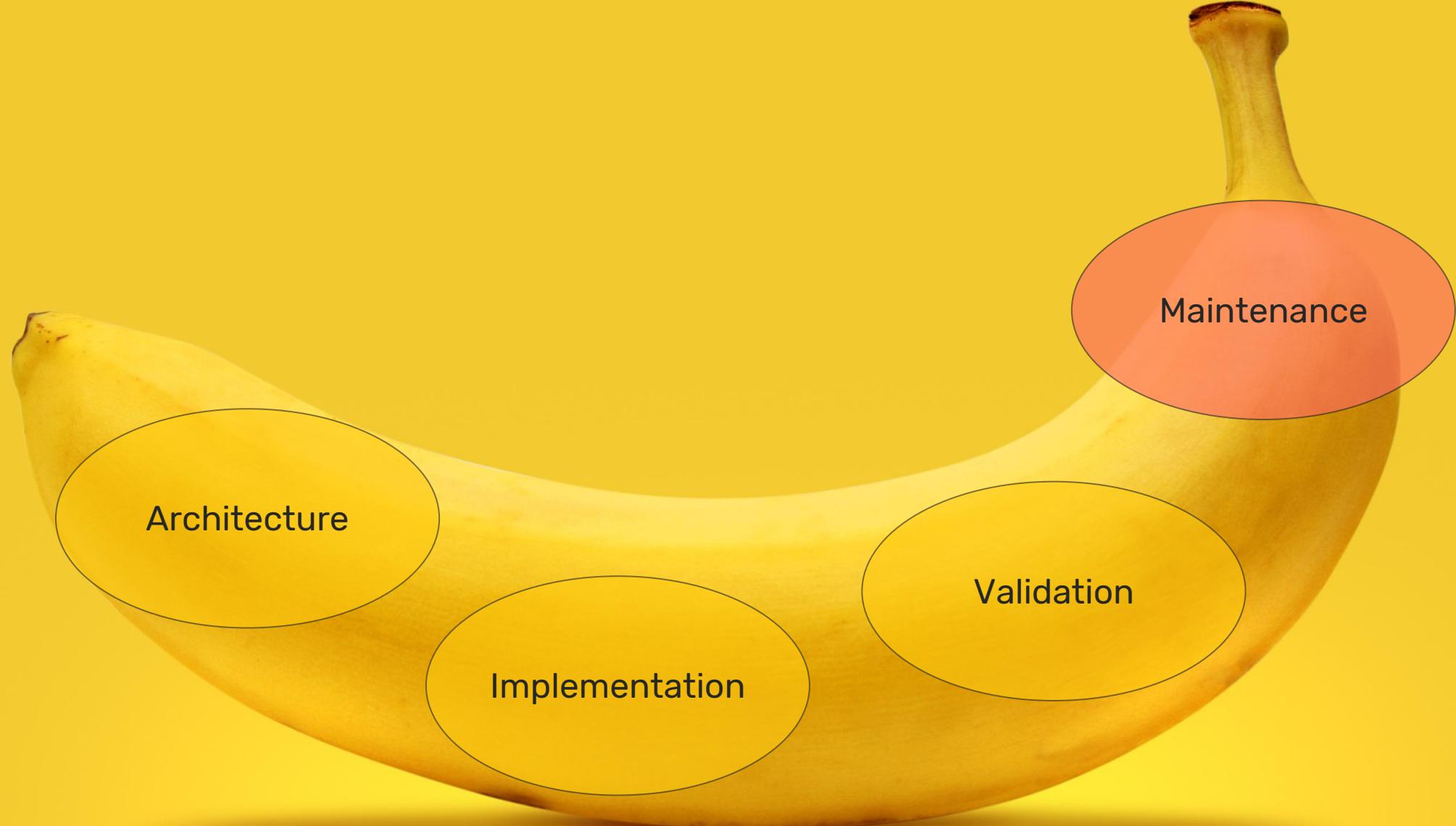

# Conclusions

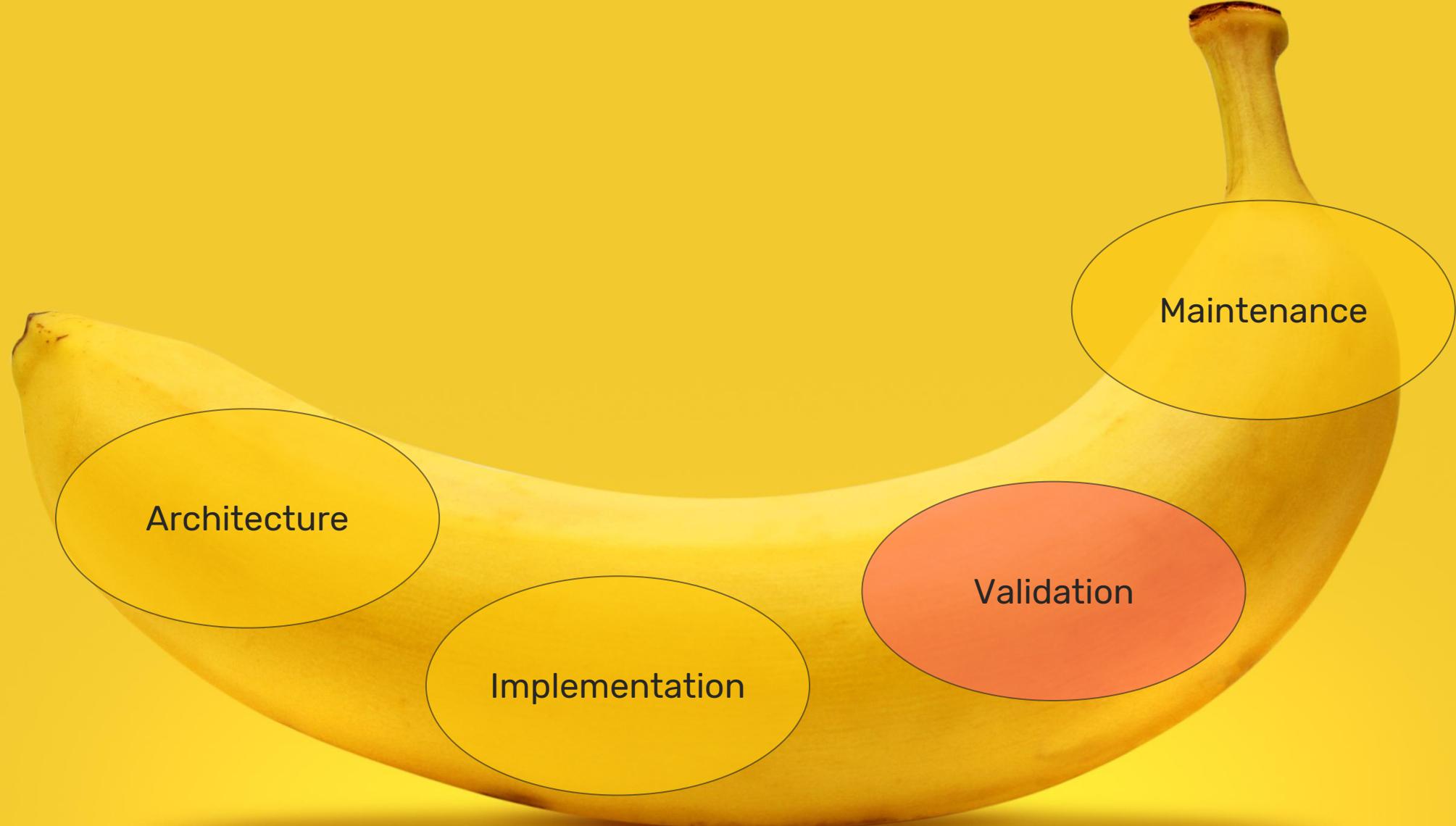

Architecture

Implementation

Validation

Maintenance

# Conclusions and Summary

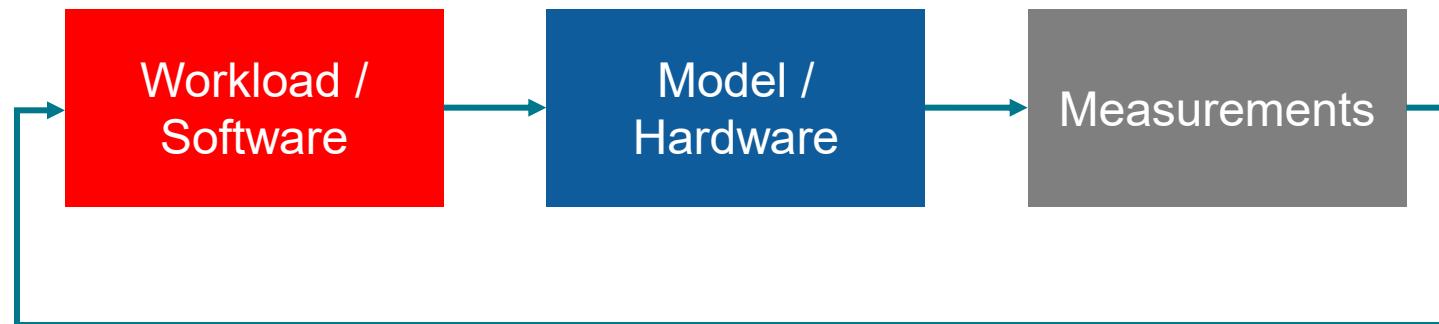

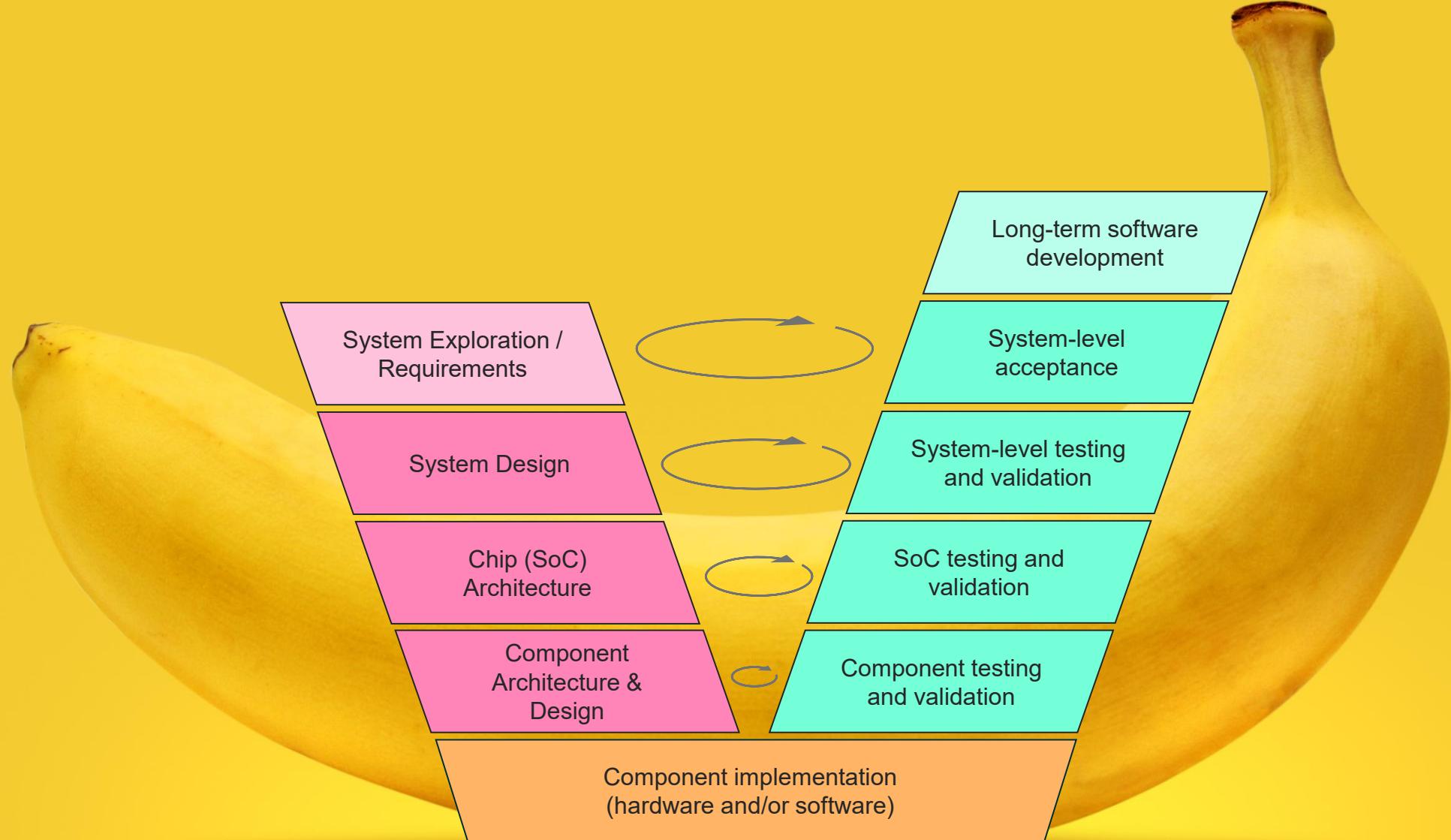

Simulation and architecture can be done at many levels

System models can extend to networks and networks-of-networks

Use cases drive simulation setups

Expect to mix models from different sources and of different types

Use the right models for the right purpose!

Simulation models should always be more flexible than reality

Watch out for feedback loops and control loops in your workloads

You can only model what you have information about!

Model usage continues through the product lifecycle

cadence®

See [www.vlabworks.com](http://www.vlabworks.com) and [www.cadence.com](http://www.cadence.com) for more about us!

© 2025 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <https://www.cadence.com/go/trademarks> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.